通过并联SiC MOSFET功率器件,可以获得更高输出电流,满足更大功率系统的要求。本章节主要介绍了SiC MOSFET并联运行实现静态均流的基本要求和注意事项。

1. 静态电流不平衡率

在SiC MOSFET功率器件并联连接的情况下,电流倾向流向VDS(on)较小的器件,此时的电流不平衡比例称为静态电流不平衡率(或稳态电流不平衡率)。电流不平衡率可用如下公式(1)来计算,其中Imax为并联支路最大电流,Imin为并联支路最小电流,Itotal为并联总电流。

2. 影响静态电流不平衡率的因素

影响静态电流不平衡率的主要因素有器件通态压降VDS(on)、主回路阻抗和温度。

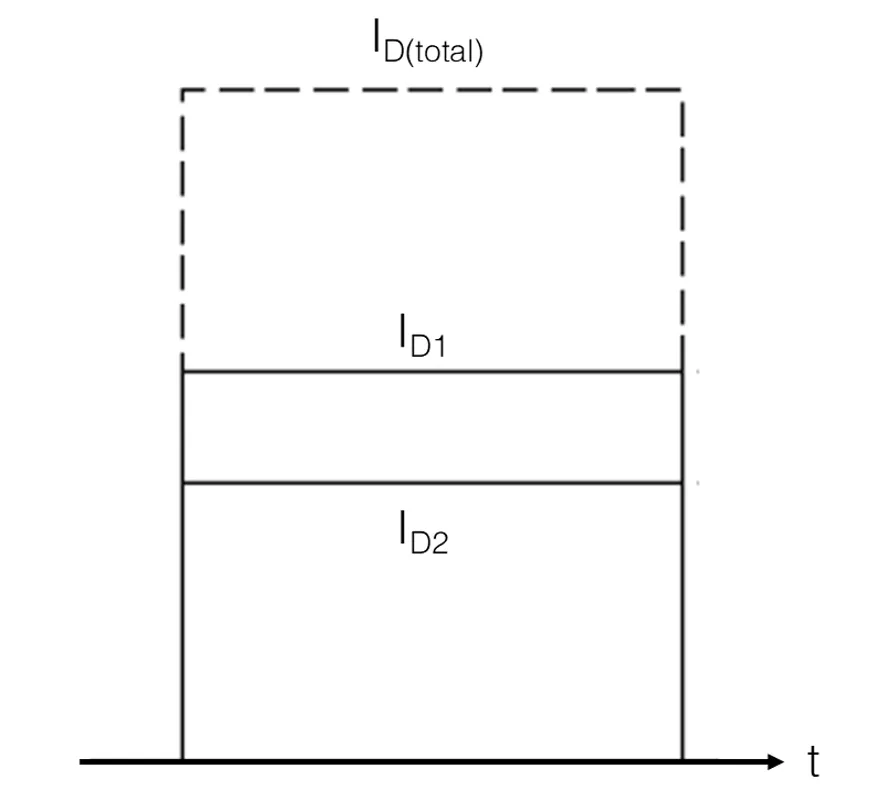

通态压降VDS(on)引起的稳态电流(di/dt≈0)不均衡如图1所示。为了减小这种电流不均衡,并联器件的VDS(on)应尽可能接近,例如采用同一批次或者特别挑选的器件。

图1:VDS(on)引起的稳态电流(di/dt≈0)不均衡

以两个SiC MOSFET器件并联为例,其rDS(on)分别为r1和r2,那么其导致的静态电流不平衡率如下式(2)所示:

并联时VDS(on)1=VDS(on)2,式(2)可变为:

假设通态电阻相差10%,也即r2=1.1r1,通过上式可以算得其静态电流不平衡率为4.8%。

实际应用中,为了满足预想的静态电流不均衡率(比如5%),可以根据式(3)反推其通态电阻差异Δr(或通态压降差异ΔVDS(on)),然后根据出厂测试报告来挑选适合并联的器件。

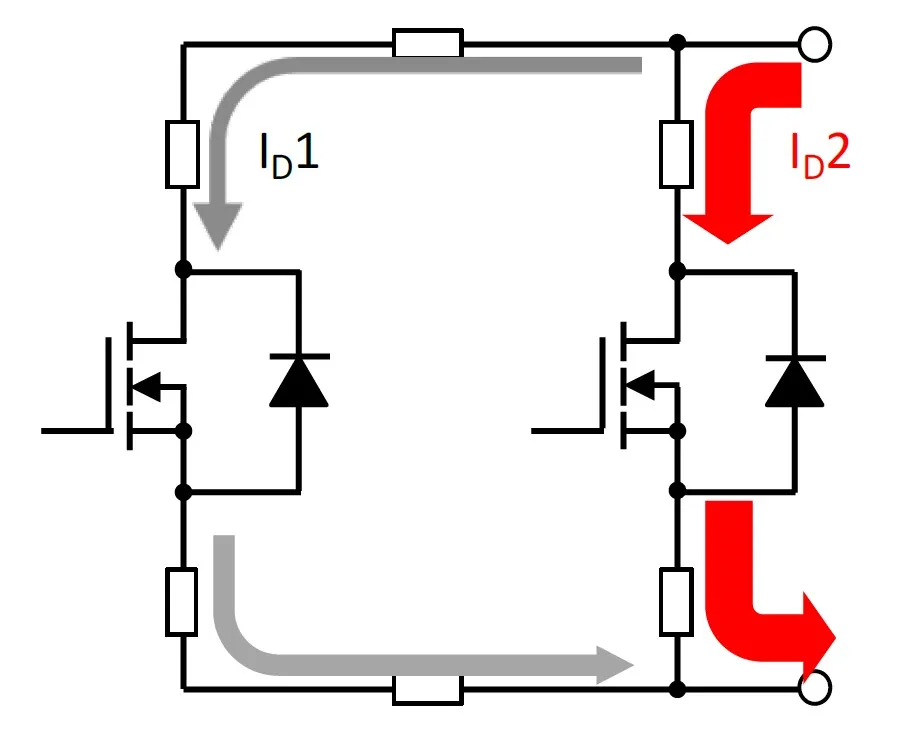

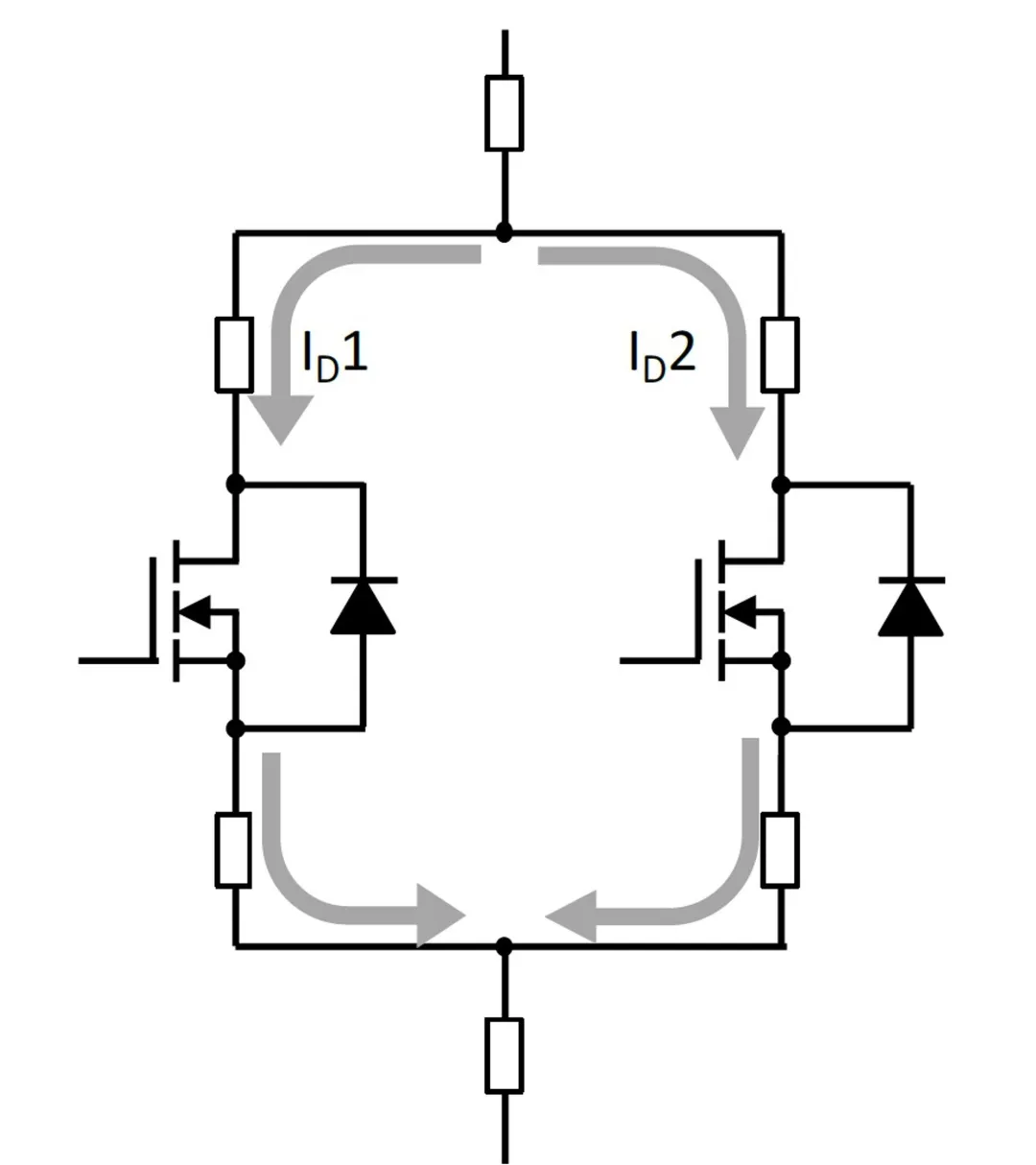

主电路阻抗不仅影响静态电流均衡,也影响动态电流均衡。主电路不对称连接如图2所示,与之相对应的图3为对称布局。

图2:主回路不对称布局(ID1<ID2)

图3:主回路对称布局(ID1=ID2)

温度不仅影响静态电流均衡,也影响动态电流均衡。温度会影响SiC MOSFET的通态电阻rDS(on),通态电阻主要包括沟道电阻、JFET电阻和漂移层电阻。沟道电阻具有负温度特性,而JFET电阻和漂移层电阻具有正温度特性,器件整体的通态电阻在高于常温时呈现正温度特性。随着SiC MOSFET温度的升高,通态电阻增大,流过的电流减小。通态电阻的这种正温度特性会抑制并联连接的电流不平衡。

3. 并联降额

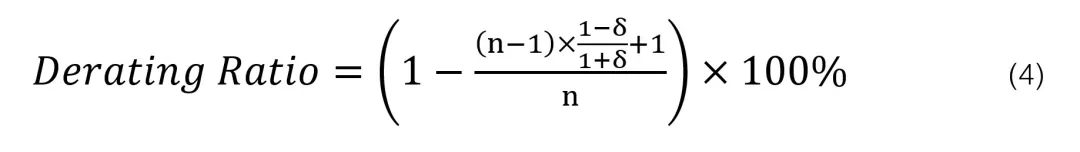

当功率模块并联时,可以使用如下公式计算降额率:

其中n为并联模块的数量,δ为静态电流不均衡率。

例如,当一个模块的额定电流值是600A,3并联,电流不平衡率δ=15%(在上述公式中δ=0.15),根据公式(4),可以得到降额率为17.4%,降额电流值=3×600A×0.174=313.2A。那么降额后的总电流值如下:3×600-313.2=1486.8A。

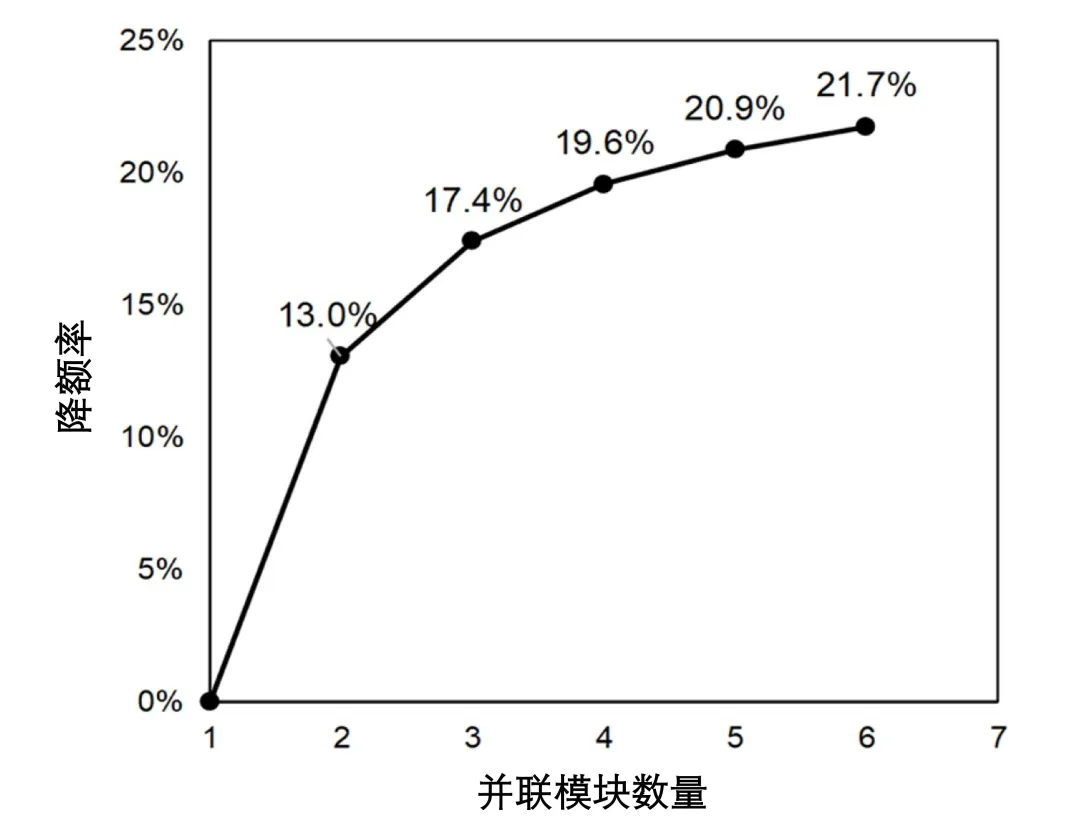

当电流不平衡率为15%时,并联模块数量和降额率之间的关系如图4所示:

图4:并联模块数量和降额率之间的关系(电流不平衡率为15%)

文章来源:三菱电机