电感器与电感线圈有何区别?

judy -- 周四, 04/15/2021 - 14:50

电感线圈和电感器区别

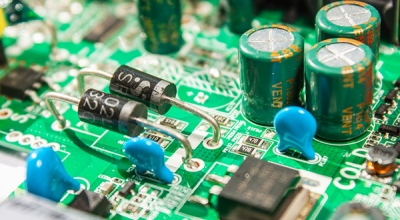

电感线圈是电感器内中的一个重要组成部分。因为电感器一般由骨架、绕组(线圈)、屏蔽罩、封装材料、磁芯或铁芯等组成。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

电感线圈和电感器区别

电感线圈是电感器内中的一个重要组成部分。因为电感器一般由骨架、绕组(线圈)、屏蔽罩、封装材料、磁芯或铁芯等组成。

随着电子设备小型化以及电路中5G信号频率快速增加,电子控制系统的传输速率和时钟频率在不断的上升和提高。

来自人体、环境甚至电子设备内部的静电对于精密的半导体芯片会造成各种损伤,例如穿透元器件内部薄的绝缘层;损毁MOSFET和CMOS元器件的栅极;CMOS器件中的触发器锁死;短路反偏的PN结;短路正向偏置的PN结;熔化有源器件内部的焊接线或铝线。为了消除静电释放(ESD)对电子设备的干扰和破坏,需要采取多种技术手段进行防范。

作为使用电感的降噪对策之一,本文将介绍使用共模滤波器降噪的内容。从严格意义上讲,共模滤波器并不是电感器,而是磁性器件,是降噪对策中的重要部件。

共模滤波器

作者:Walter N. Maclay, 总裁, Voler Systems,文章转载自:Digi-Key

USB是技术应用的最成功案例之一。在过去20年来,USB通用标准一直都是有线数据和电源传输的中心。但是近年来,由于USB 3.x的标准具有多种不同电缆类型,使得情况变得有些混乱。另外,将多个连接标准纳入其中的一部分,这也变得更加令人困惑。

对学电子的人来说,在电路板上设置测试点(test point)是在自然不过的事了,可是对学机械的人来说,测试点是什么?

Murata Electronics快速充电噪声抑制解决方案有助于限制快速充电器产生的噪声,提高接收范围和速度。由于快速充电系统采用直流-直流转换器,因此直流-直流转换器产生的开关噪声会导致接收灵敏度降低。减少直流-直流转换器产生噪声的有效方法是将铁氧体磁珠插入输出部分。

快速充电噪声问题

本文转载自:电子电路设计

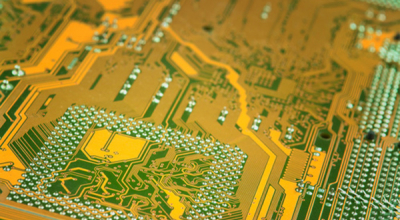

随着电子技术的高速发展,以及无线通信技术在各领域的广泛应用,高频、高速、高密度已逐步成为现代电子产品的显著发展趋势之一。信号传输高频化和高速数字化,迫使PCB走向微小孔与埋/盲孔化、导线精细化、介质层均匀薄型化,高频高速高密度多层PCB设计技术已成为一个重要的研究领域。本文,我们主要来了解下高频PCB设计的一些实用技巧。

高频PCB