引 言

RISC-V架构以其开放性和高度可定制的特性,正在重塑处理器设计格局。然而,这种灵活性也带来了显著的验证挑战,使其验证复杂度远超传统固定架构处理器。

RISC-V的验证难点主要体现在四个方面:首先,微架构灵活性极大增加了验证复杂性。不同的内存层次设计、流水线结构以及功耗时序约束,使得验证空间呈指数级扩张。其次,自定义指令集显著扩大了验证范围。每条新增指令都需要在各种操作条件下进行全面验证,大幅增加验证工作量。

第三,模块化ISA带来了兼容性挑战。针对特定扩展集编译的程序可能无法在不支持相关扩展的处理器上运行,这对互操作性验证提出了更高要求。最后,缺乏统一参考模型导致实现不一致性问题,不同团队对规范的理解差异可能产生不同的实现行为。

综上所述,RISC-V验证面临规模、范围和一致性的多重挑战,传统验证方法已难以胜任。迫切需要更先进的验证方法学与平台,这也正是本白皮书后续将要深入探讨的重点。

1. RISC-V 验证接口 (RVVI)

1.1 应对RISC-V验证复杂性的解决方案

RISC-V处理器因其灵活性而带来的验证挑战,亟需一种标准化、可复用的验证方法。为应对这一需求,RISC-V验证接口(RVVI)应运而生。RVVI是一种开放标准接口,旨在为RTL设计、测试平台环境与RISC-V验证IP(VIP)之间提供统一的通信框架,从而显著提高验证效率与可重用性。

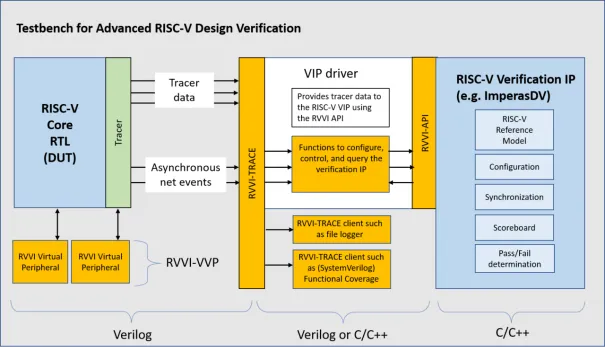

1.2 RVVI的关键组成部分与工作机制

RVVI定义了一系列标准化接口与协议,包括指令流跟踪、执行行为比较和状态同步等关键机制。通过引入指令追踪器(Tracer),RVVI可有效处理乱序执行和推测执行等复杂场景,并支持与参考模型进行实时比对,确保实现与架构定义的一致性。

该接口还支持功能覆盖率收集与ISA符合性检查,为验证闭环提供坚实基础。借助RVVI,工程师能够构建高度可复用的测试平台,显著缩短验证周期,加速设计验证(DV)流程。

图1 用于先进RISC-V设计验证的测试平台

2. 纯仿真环境中 RVVI 的局限性

尽管RVVI在仿真环境中发挥了重要作用,但其在纯软件仿真模式下仍存在若干本质性局限。首先,指令跟踪、行为比对与监控操作带来显著的性能开销,仿真速度成为测试吞吐量的瓶颈——即便是一些基础测试用例,其运行时间也可能超出合理范围。

其次,由于缺乏高效的时钟同步机制,待测设计(DUT)与参考模型之间可能出现时序不同步的问题,影响验证准确性。更关键的是,RVVI在系统级建模方面存在不足,无法为包含操作系统启动、设备初始化及外设交互在内的全芯片级(SoC)场景提供有效支持。

此外,当设计包含自定义扩展指令时,为兼容RVVI标准所需的基础设施改造不仅带来额外维护负担,还可能引入新的验证漏洞。这些因素共同限制了RVVI在纯仿真环境中处理复杂SoC工作负载的能力。

3. 解决方案:基于事务级的加速 (TBA)

面对RISC-V处理器在验证效率、设计规模及系统复杂度方面的多重挑战,基于事务级的加速(Transaction-Based Acceleration, TBA)已成为应对这些问题的关键解决方案。TBA通过提高验证抽象层级,突破传统周期精确仿真的性能限制,显著提升验证吞吐量,尤其适用于当前日益复杂的SoC及支持自定义扩展的RISC-V设计。

TBA采用事务级建模(Transaction-Level Modeling, TLM)接口与专用通信协议,建立起软件测试环境与硬件设计之间的高效协作机制。与传统的逐周期信号交互方式不同,TBA将诸如DMA传输、存储器读写等多周期操作封装为完整事务,在更高抽象层级完成数据交换。这种方式极大减少了软硬件间所需传输和处理的数据量,测试平台通过总线功能模型(BFM)以事务为单位与硬件进行通信,在提升效率的同时也降低了验证环境的整体复杂度。

在体系架构层面,TBA明确划分了软硬件验证功能:硬件侧集成了可综合的HDL设计,包括被测设计(DUT)、总线功能模型(BFM)以及时钟与复位生成模块;软件侧则承载非时序相关的测试任务,包括测试控制、激励生成、参考模型、检查机制及覆盖率收集。这种分区策略充分发挥硬件执行高速性与软件灵活性的双重优势,为构建高效系统级验证环境奠定基础。

TBA不仅在高吞吐量并行执行方面表现优异,还具备多方面的显著优势:

· 验证速度大幅提升:TBA可实现较传统RTL仿真10–1000倍的加速效果。其多时钟周期事务处理机制避免了逐周期仿真开销,显著缩短验证周期,加快产品上市时间(Time-to-Market, TTM),并支持更高效的回归测试

· 早期软件开发与验证:TBA支持软硬件协同开发,软件团队可在流片前进行驱动和固件验证,大幅缩短系统集成时间,降低项目风险

· 卓越的可扩展性:TBA能够高效处理超大规模SoC和ASIC设计验证,克服了传统RTL仿真在规模和性能方面的局限性

· 调试与验证效率提升:TBA支持事务级调试,无需追踪大量信号和周期,极大简化错误定位过程。内置协议检查器可自动检测违规操作,参考模型能够与实际RTL输出进行实时比对,确保设计符合预期。软件端覆盖率收集与分析功能更全面保障验证完备性

TBA不仅在特定验证场景中表现突出,更在通用验证环境中展现出广泛的应用价值。其通过重构验证效率边界,为现代复杂芯片设计提供了关键的技术支撑,已成为验证流程中不可或缺的重要组成部分。

4. 基于事务级的加速 (TBA) 在 RVVI 中的应用

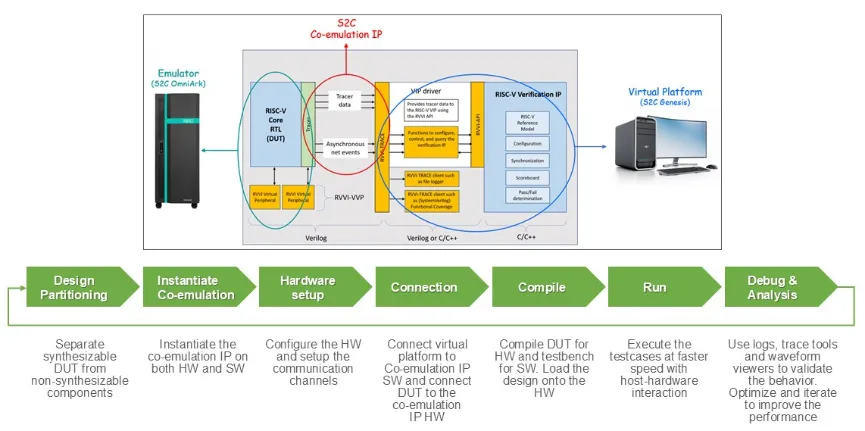

为充分发挥事务级加速(TBA)在RISC-V验证中的效能,其与RISC-V验证接口(RVVI)的高效集成尤为关键。该集成方案通过系统级协同仿真架构,在保持RVVI规范要求的周期精度的同时,大幅提升验证效率与系统可扩展性。

在实际应用中,该系统采用分区的测试平台架构:虚拟平台负责运行参考模型、RVVI检查器及覆盖率收集模块,而RISC-V核心则部署于仿真加速平台(如思尔芯的芯神匠架构设计软件和芯神鼎硬件仿真系统)中运行。这种架构既保留了软件环境的灵活性与可调试性,也充分利用了硬件仿真平台的高速执行能力。

为实现跨平台的高效协作,协同仿真IP利用TBA技术建立起稳定、高带宽的通信信道。TBA的事务级抽象机制不仅有效降低了通信开销,还确保了芯神鼎硬件仿真系统与芯神匠架构设计虚拟平台间的精确同步,从而在分布式系统中维持严格的时间精度与一致性。该通信层能够可靠地传输RVVI所需的指令执行轨迹、内存访问记录等关键跟踪信息,确保在指令集仿真器(ISS)与硬件仿真系统之间实现无缝的状态比对与行为验证。

通过TBA与RVVI的深度融合,验证团队能够在享受事务级加速带来的性能提升的同时,继续遵循标准化的验证接口与流程。这不仅显著加速了复杂验证场景的运行,如操作系统启动、多核同步及异常处理测试,也为具有自定义扩展的RISC-V处理器提供了高效且可重用的验证解决方案。

图2 TBA+RVVI流程

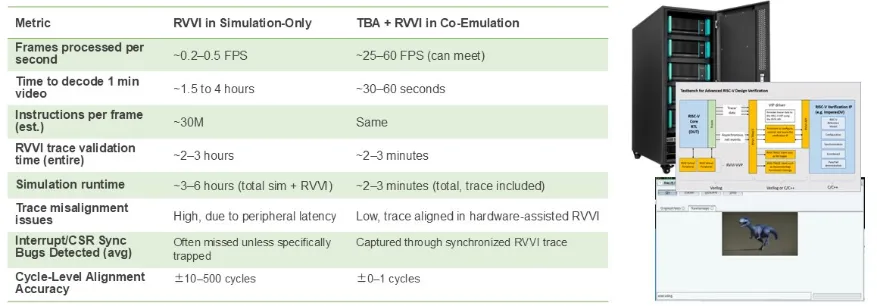

通过在视频处理(分辨率:320×180)用例中的实际验证,基于TBA与RVVI的协同仿真架构展现出显著成效。测试结果显示,该方案在维持RVVI周期精度的同时,实现了较传统仿真方法25倍以上的加速效果。视频处理流水线中的帧缓存管理、像素运算及数据传输等关键操作均得到充分验证,其处理吞吐量完全满足实时性要求。

值得注意的是,在此类数据密集型应用中,TBA通信信道的高带宽与低延迟特性有效避免了仿真瓶颈,确保了视频帧处理的连贯性与完整性。同时,RVVI接口成功捕获到所有自定义指令的执行轨迹,验证了其在实际应用场景中的兼容性与可靠性。覆盖率分析表明,功能覆盖率达到98.5%,有效保证了验证的完备性。

图3 视频处理(分辨率:320×180)用例

这一结果充分证明了TBA与RVVI相结合的方案在处理具有高数据吞吐需求的复杂SoC设计中的实用价值,为同类多媒体处理芯片的验证提供了高效、可靠的解决方案。

文章来源:思尔芯