本文要点

集成电路的电源完整性通常是从 PCB layout 的角度讨论,但芯片内部的电源分配网络(PDN)同样需要经过合理设计。

超大规模集成电路(VLSI)设计也将目标阻抗作为设计指标,旨在确保稳压电路单元的稳定供电。

集成电路版图中的寄生效应会影响 PCB 的电源完整性和信号完整性。

在高速数字系统成为主流之前,电路板和集成电路电源轨上经常会使用设计拙劣的电源分配网络(PDN),阻抗高达 250 毫欧。这个阻抗值看似很小,并且在 20 世纪 90 年代的时候并不会造成严重问题。在当时的系统中,逻辑电平的噪声容限足够低,上升时间足够缓慢,使得开关事件期间电源轨上的瞬态响应基本难以察觉。直到 ECL 电路问世,工程师们才意识到无论是 PCB 还是集成电路都面临电源完整性挑战。

在超大规模集成电路(VLSI)设计中,集成电路需要低阻抗电源轨的原因与 PCB 如出一辙。但对于 PCB 而言,有充足的空间来实施使用平面层和多个电容器等策略。这些策略在集成电路中则难以实施,因为空间极其宝贵且 VLSI 对设计架构有限制。在 VLSI 设计和现代集成电路结构中,有一些简单的方法可以分析电源完整性,其核心都关乎电报方程和麦克斯韦方程组的通用数学语言。

在超大规模集成电路设计中,每个 BGA 集成电路都需要达到良好的电源完整性

VLSI 电源完整性的基础

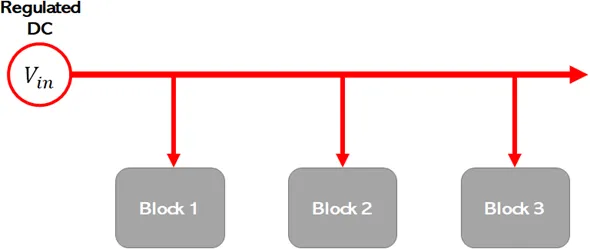

当今的超大规模集成电路设计采用总线架构,将电力从电源输入端分配到设计中的各个模块。这些总线架构与典型 PCB 上的电源分配网络存在显著差异。下图展示了 PCB 上电源总线的结构框图,其中电源被分配至半导体裸片上的多个功能模块。

VLSI 中典型的电源分配网络架构

集成电路的情况可能更为复杂,某些器件需要多电压供电,因此会配置多条电源总线为不同电路模块分别供电。在 PCB 的电源分配网络中,并不总是存在被分隔成不同稳压器部分的总线架构。

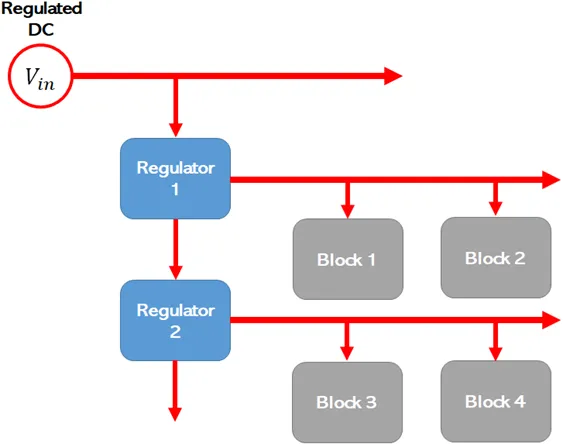

与集成电路电源分配网络上采用的典型总线架构不同,PCB 通常采用级联式稳压器架构,通过逐级降压将系统电压转换为多个逻辑电平(通常为 5V、3.3V、1.8V 和 1.2V)。虽然某些集成电路会内置稳压器(通常为 LDO)来提供固定电压,但不会像 PCB 那样采用多级稳压器串联的级联方案。作为对比,下图中展示了这种架构。

PCB 中典型的电源分配网络架构

从上图可以明显看出,PCB 中的电源分配网络结构可能相当复杂,而集成电路中的总线结构相对简单,因此更易于分析。尽管不同类型系统中的 PDN 结构可能各不相同,但理解与分析各类系统时都会运用到一些通用的理论和概念。VLSI 目标阻抗

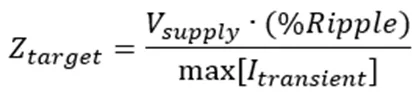

超大规模集成电路设计仍将目标阻抗概念作为设计目标。换言之,设计目标是将阻抗值最小化,确保到达设计中各个电路模块的电压尽可能稳定。根据欧姆定律,当数字电路模块工作时,电源分配网络的电压变化与其阻抗及流入网络的电流直接相关。

目标阻抗方程

只需输入供电电压、期望纹波值和预期电流消耗,即可得出所需的 PDN 目标阻抗。上述方法通常通过 SPICE 仿真(基于 FET 电路模型)来实现,得出晶体管电路中每次开关事件的总电流消耗。一旦获知 PDN 阻抗,即可设计主要电源轨以确保稳定供电。

设计 PDN 阻抗

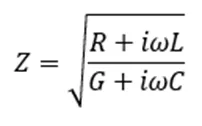

处理 PDN 汇流排的标准方法是,在平面半导体基板的主要接地平面上方使用传输线模型。优秀的集成设计设计软件会包含特定半导体材料的相关介电常数值,通过计算标准传输线阻抗参数即可确定电源轨阻抗:

电源轨目标阻抗方程

优秀的 PCB layout 与集成电路布局设计工具能够根据电源轨的几何结构,计算出上述阻抗方程中的各项参数值。确定阻抗值后,应将其与目标值进行比对,以便最大限度缓解工作期间电压跌落。其他技巧包括使用电源轨的网络参数,例如 Z 参数或 ABCD 参数。

到目前为止,我们只是从电源轨方面讨论了 VLSI 电源完整性。那么封装方面呢?事实证明,集成电路封装中有一种现象会影响集成电路和 PCB 设计的电源完整性——那就是地弹。

地弹

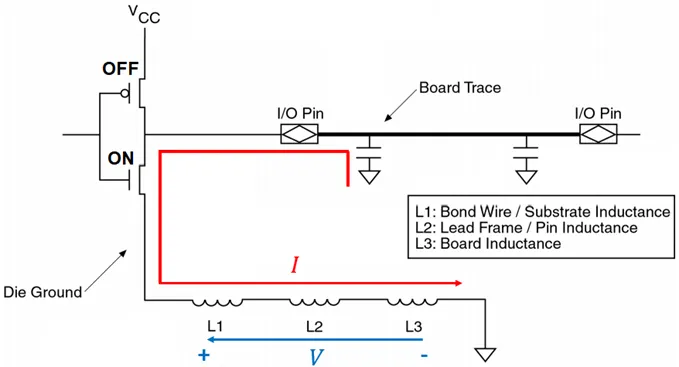

SSN 同步开关噪声(PCB 设计人员更常用的术语是“地弹”)既属于集成电路封装问题,也属于电路板布局问题。从半导体裸片延伸至封装引线框架的键合线,以及裸片和封装上的所有焊盘均存在一定电感。当多个 I/O 端口同时切换时,这种电感会导致 I/O 端口上出现电压尖峰。

导致电感和地弹的三个因素中有两个源于集成电路封装

采用 flip chip 倒装芯片封装可部分解决这两个封装问题,因为此类封装无需使用键合线。对于返回到 PCB 接地层的连接,电路板上的过孔电感也会增加其寄生电感。除了使用旁路电容外,优秀的 CAD 工具还能按照您的要求放置带封装的集成电路,从而有效抑制设计中的地弹现象。

Cadence Sigrity X 工具套件可帮助您轻松应对超大规模集成电路和 PCB 的电源完整性问题——新一代 Sigrity 解决方案重新定义了 SI 和 PI 分析,将性能提高了 10 倍,同时保持了 Sigrity 工具一贯的准确性;提供一整套时域和频域仿真功能,可确定目标阻抗是否需要降低;可用于 PDN 阻抗分析的仿真功能更能全面评估系统功能,并确保设计的电源完整性。

文章来源:Cadence