作者:电子创新网编辑部

AI 的算力需求正在以“倍增”的速度席卷半导体产业。大模型训练、推理负载让 GPU 和 AI 加速器的 带宽瓶颈日益显现。传统 SoC 集成方式正在走向极限,摩尔定律的脚步放缓,封装互连反而成为“突围”的关键。

在这一背景下,总部位于硅谷的 Sarcina推出了基于 UCIe-A(Advanced)与 UCIe-S(Standard) 的 32 GT/s 芯粒互连方案,并在中介层(RDL Interposer)和有机基板两个层面同时实现突破。

这不仅是一次技术迭代,更是一次封装工程的突围。

为什么是“突围”?

过去十年,AI 芯片的算力增长主要靠晶体管堆叠与先进工艺。但今天,工艺缩放收益递减,单片 SoC 变得过大、过贵、良率下降。

瓶颈 1:带宽 —— 芯片计算单元愈发强大,但数据互连跟不上,AI 引擎常常处于“等待状态”。

瓶颈 2:成本与良率 —— 超大 SoC 的制造成本远超预期,良率下降拖累量产。

瓶颈 3:工艺代差 —— 先进制程不适合所有模块(例如模拟、电源管理、I/O),导致设计受限。

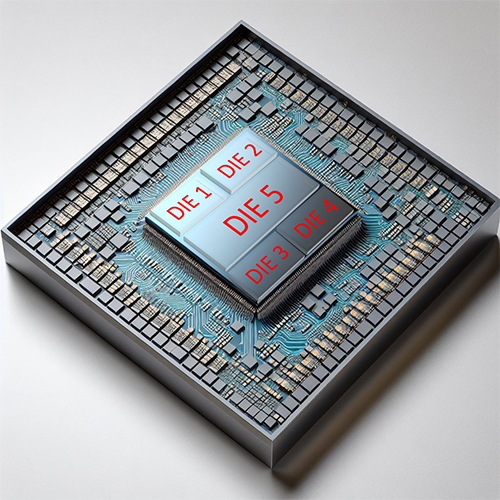

突围的路径就是芯粒化(Chiplet)。但芯粒化要成功,关键在于能否构建一条高带宽、低串扰、低功耗的互连高速公路。

这就是 UCIe(Universal Chiplet Interconnect Express)的使命。

Sarcina 的答案:UCIe-A 与 UCIe-S 双路径

1. UCIe-A —— 中介层上的极致性能

Sarcina 通过优化 RDL 中介层,带来了:

32 GT/s 芯粒间速率,完全符合 UCIe 2.0。

独特的 “beach front” 设计:在芯片边缘形成超紧凑 3D 布线区域,最大化空间利用率。

显著降低串扰,在有限铜层下实现可制造性与信号完整性的平衡。

简言之,UCIe-A 是面向 AI/HPC 芯片核心加速引擎 的高速通道,追求极致性能。

2. UCIe-S —— 基板上的系统延展

Sarcina 同时在有机基板与 HDI PCB 上推进 UCIe-S 方法学:

低插入损耗与低串扰,支持更长距离互连。

紧凑 3D 多层布线,让芯片边缘能高密度堆叠模块。

已通过 32 GT/s 仿真验证,并为 UCIe 3.0 预作铺垫。

它面向的是 系统级集成:加速模块、PCIe 子卡、主板互连……让 UCIe 不止存在于芯片内部,而是贯穿整个系统封装。

为什么重要?

Sarcina 的 UCIe 技术不只是速度的提升,而是封装产业的三大共鸣点:

1. 性能突围

32 GT/s 意味着下一代 AI 芯片不会再因为互连瓶颈而“算力闲置”。

2. 制造突围

减少 RDL 层数、提高良率,意味着这种设计可以 量产,而不是停留在实验室。

3. 系统突围

不止于单芯片,UCIe-S 打通基板与系统,让封装成为真正的 系统级基建。

中国市场的启示

对于国内 AI 芯片厂商而言,计算架构与工艺不是唯一战场。先进封装与互连 已经成为下一轮竞争的核心。

Sarcina 的路径启示我们:

不能只追求性能,还要考虑 成本、良率与制造可行性。

未来的差异化,不仅在算力本身,而在 算力如何被高效释放。

封装设计公司将成为 AI 芯片产业链中的 关键角色,甚至可能决定产品能否落地。

结语

正如 Sarcina CEO Larry Zu 所言:“我们不仅在设计互连,更是在为下一代 AI 系统奠基。”

32 GT/s 的 UCIe 突围,不仅是一次封装的优化,更是 AI 系统未来能否持续进化的关键。

在摩尔定律日渐式微的今天,谁能掌握芯粒互连的主动权,谁就有可能在下一轮 AI 算力竞争中占据先机。

注:本文为原创文章,转载需注明作者、出处及原文链接,否则,本网站将保留追究其法律责任的权利。