问:Δ-Σ ADC 模数转换器抗混叠滤波器组件选择

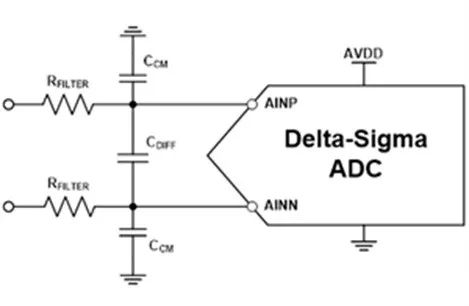

低速 Δ-Σ ADC 通常需要一个简单的单极 RC 滤波器来减少混叠效应。对于差分信号,滤波器结构通常由两个滤波路径组成:一个差分滤波器(源自两个滤波器电阻 RFILTER 和差分电容器 CDIFF 的组合);和一个共模滤波器(源自一个滤波器电阻 RFILTER 和共模电容器 CCM 的组合)。这如图 1 所示。

图 1:低速 Δ-Σ ADC 的抗混叠滤波器结构

[注意:如果您有一个单端输入,其中 AINN 是接地参考,则滤波器将由 RFILTER 和 CCM 组成。但是,设计指南将与下面描述的 差分 滤波器的设计指南相同。]

为了确定图 1 中每个组件的值,将分析分为三个部分会有所帮助:

对于每个问题,ADS124S08 (24 位、12 通道、4kSPS Δ-Σ ADC)将用作示例数据转换器,以帮助说明如何将这些设计原则付诸实践。

差分滤波器截止频率应该是多少?

抗混叠滤波器的目的是将频率内容保持在 ADC 调制器频率 (fMOD) 或附近,使其不再混叠回传通带,因为这些频率不会被数字滤波器本身拒绝。因此,请设置差分滤波器的 3dB 截止频率 fC-DIFF,使其比 fMOD 低 10 到 100 倍。这将分别导致 fMOD 周围出现 20dB 至40dB 的频率抑制。所需的抑制量取决于系统的设计目标。如果您想了解有关抗混叠滤波器基础知识的更多信息,以及您应该关注调制器频率混叠的原因。

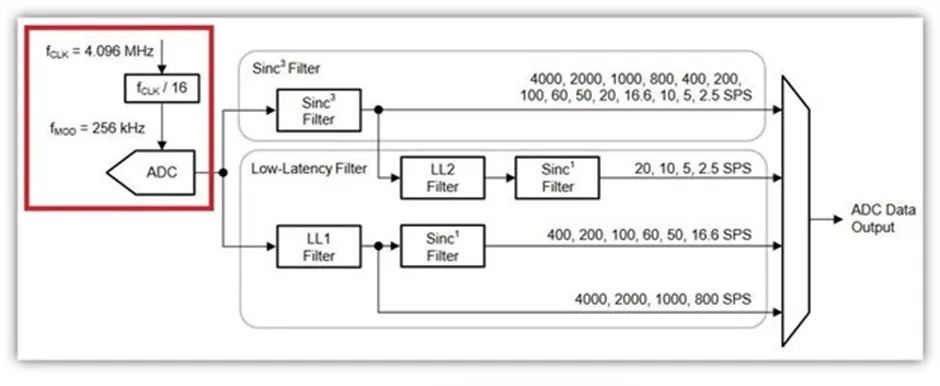

对于 ADS124S08,fMOD 为 fCLK/16,其中 fCLK 是主时钟频率,如图 2 所示。给定标称内部振荡器频率 4.096MHz 后,fMOD = 4.096MHz/16 = 256kHz。因此,对于这个特定的 ADC,可以选择fC-DIFF = 2.56kHz 或 fC-DIFF = 25.6kHz,以分别获得 20dB 或 40dB 的抑制。此外,请确保 fC-DIFF 也大于数字滤波器的 -3dB 频率 f3dB,否则 RC 滤波器会影响数字滤波器特性。

图 2:ADS124S08 数字滤波器结构和调制器时钟

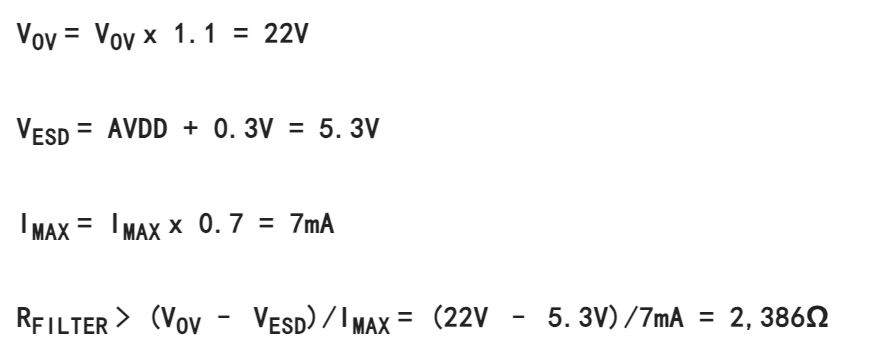

我应该选择多大阻值的滤波电阻器?

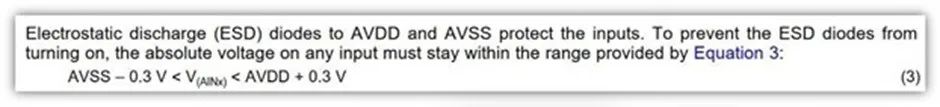

在图 1 所示的系统中,滤波电阻器也用作电流限制器。因此,该电阻器的尺寸可限制最大引脚输入电流 (IMAX),如 ADC 的绝对最大额定值表所示。要确定此电阻上允许的压降,您需要在系统输入 (VOV) 上看到预期过压条件以及 ADC 集成 ESD 保护二极管 (VESD) 的接通电压。然后,您可以使用以下公式来求解电阻器值 RFILTER:

对于 ADS124S08,IMAX 为 10mA。如图 3 所示,当输入电压超过模拟电源 300mV 时,ADS124S08 的ESD 二极管会导通。

图 3:ADS124S08 的 ESD 信息

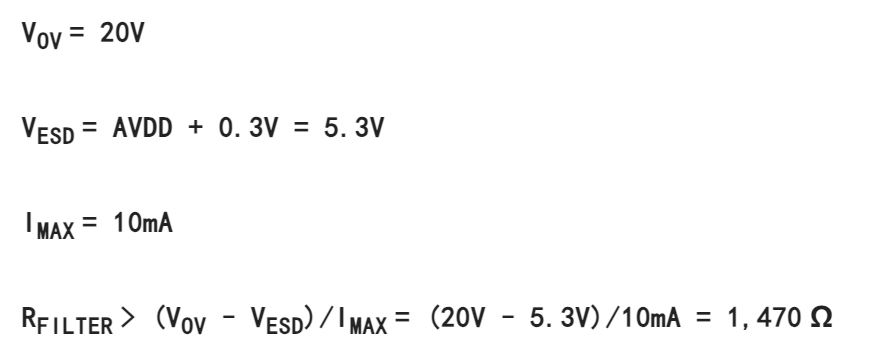

如果您假设 AVDD = 5V,并且预期的最大过压条件 VOV 为 20V,那么您现在可以获得确定 RFILTER 最小阻值所需的全部信息:

请注意,在给定系统参数的情况下,这是电阻器可用于限制进入 ADC 引脚的电流的绝对最小值。妥善做法是在计算电阻器阻值时,允许过压条件和最大电流有一定的裕量。这可确保提供更强大的保护电路,以适应任何潜在的系统变化。例如、您可以假设 VOV 的容差为 10%,IMAX 的容差为 30%:

计算适当的电阻值后,选择一个等于或大于该值的标准电阻器。

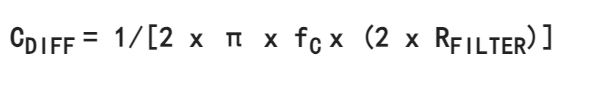

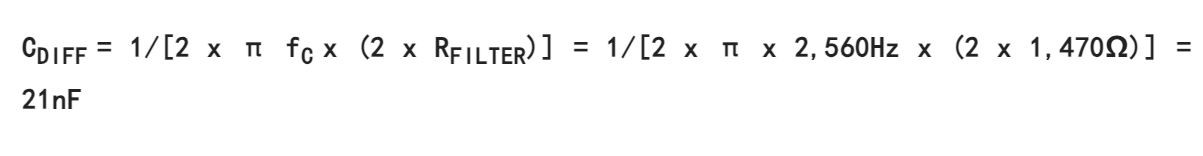

我应该选择多大容值的差分和共模电容器?

由于您已经确定了滤波器截止值和电阻器阻值,因此可以使用以下公式来确定差分滤波器 CDIFF 的电容器容值:

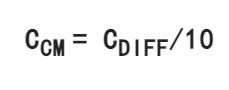

然后选择共模电容器 CCM,使其比 CDIFF 小 10 到 20 倍,这样:

给定之前确定的 RFILTER 和 fC-DIFF 值后,您可以按如下所示计算电容器值:

本文转载自:得捷电子DigiKey