作者:Paul McLellan,来源: Cadence楷登PCB及封装资源中心微信公众号

Cadence员工Mohamed Naeim 博士曾在CadenceLIVE 欧洲用户大会上做过一场题为《2D/3D 热分析和三裸片堆叠设计实现》的演讲,本文将详细讲述该演讲内容。

实验:两个裸片是否优于一个裸片?

由于线长缩短,3D-IC 会减少功耗,带来性能提升。在此,3D-IC 指的是将一个裸片(或两个)摆放在另一个裸片之上,而不是指基于中介层的设计。在这种情况下,由于两个裸片之间的热量不易散出,将两个裸片堆叠在一起会导致温度升高。3D 热分析建立在对每个裸片进行热分析的基础之上,因此必须要先进行有效的 2D 热分析。

上图是实验设置。使用 Cadence Voltus IC Power Integrity Solution 生成用于热仿真的功耗图,然后再用 Celsius Thermal Solver 生成热功耗图。这样就能对功耗、压降和电子迁移进行兼顾热影响的分析。

使用的实验设计是一个多核心集群,有 256 个 32 位 RISC-V 内核,无 L2 高速缓存,和一个 MemPool 组。该集群有 200 万标准单元和 384 个内存宏。由于线长较短,简单地将设计随意一分为二,的确可以实现 3D-IC 设计的性能提高,但正如预期的那样,与 2D 基线(将整个芯片设计成一个裸片)相比,温度有所升高。

可以采用三种方法来改善这种情况:

1. 改进封装和冷却技术

2. 不要按 1:1 的比例拆分设计,而是将存储单元放置在逻辑单元上 (Memory-on-Logic ,MoL)

3. 或者反过来,将逻辑单元放置在存储单元上 (Logic-on-Memory,LoM)

上图左侧显示的是基线(全部位于一个裸片上),右侧显示的是相应的 3D 设计,整个设计对半拆分成顶部和底部裸片。

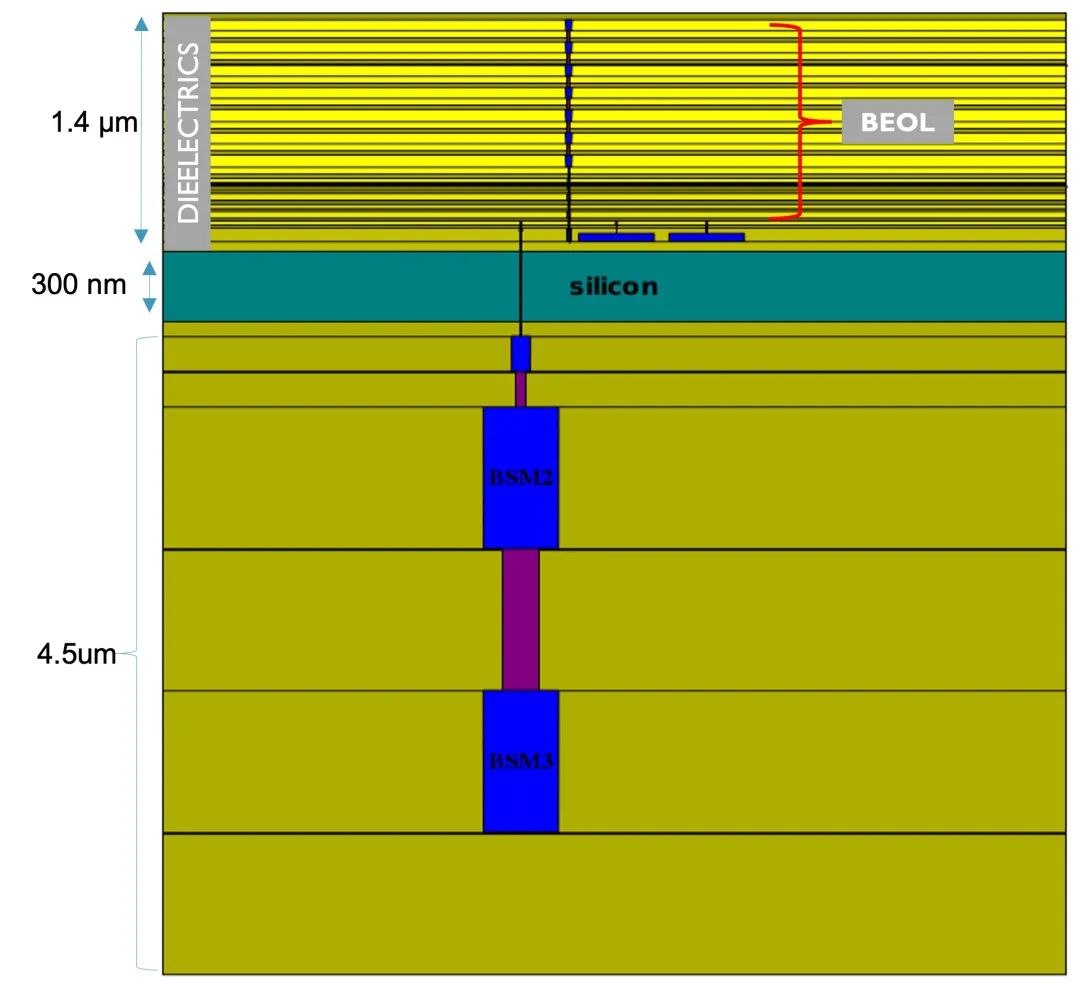

上图是 3D 版本中各层的堆叠方式。底部裸片的基板厚度为 300 纳米,总厚度为 6.2 微米。底层裸片有一个背面电源分配网络 (Backside Power Delivery Network ,BSPDN)。顶部裸片没有背面金属,硅基板厚度为 500 微米,BEOL 厚度为 1.4 微米,总厚度为 501.4 微米。这是一个普通的正面电源分配网络。

这不仅仅是两个裸片那么简单。底部有 PCB,还带焊球,顶部有散热器和散热片,中间还有键合层。

实验结果

以 1.5GHz 的工作频率进行功耗密度评估,在活动性为 10% 时进行静态功耗分析。逻辑裸片的功耗密度因更小的 footprint 和缓冲器的插入而有所增加。逻辑裸片的功耗密度比 2D 基线设计高 2.15 倍。

将 2D-Mix、MoL 和 LoM 进行比较,不难看出:由于采用了 BSPDN,底层裸片基底为 300 纳米。对于采用 MoL 和 LoM 的 3D-IC,其最高温度分别提高了 29.9°C 和 27.2°C(见上图)。

三裸片堆叠

之所以采用堆叠三个而非两个裸片的设计,是因为系统级芯片(SoC))以存储器为主导。例如,一个拥有 L1 高速缓存、64 个内核、4 个 DMA 通道和 128 位宽 L2 高速缓存的多核 SoC,存储器就占了 68% 的硅面积。

将三个裸片堆叠在一起,可以让更多存储器宏位于上层裸片上,从而改善 PPA。

上图展示了如何使用 Cadence Integrity 3D-IC 工具实现三裸片堆叠设计。

如上图所示,它属于存储器-存储器-逻辑堆叠,上面两个裸片上只有存储器。这项工作仍在进行中,因此 Mohamed 尚未报告功耗和散热结果。

结论

1. 与 2D 基线相比,3D 设计的温度更高

2. LoM 的最高温度比 MoL 的最高温度低 2.7℃

3. 在 3D-IC 设计中考虑热效应非常重要:

a. 兼顾热影响的压降(增加 4.7%)

b. 兼顾热影响的电源网络阻抗(增加 2.8%)

4. 多裸片(两个以上)堆叠有望解决“内存墙”(Memory Wall) 瓶颈

下一步是为大型 SoC 实现三裸片堆叠,并进行全面的热分析。

这些多裸片堆叠的最终结果是将 PPAC 变为 PPACT(功耗、性能、面积、成本、温度)。