随着高性能半导体需求的不断增加,半导体市场越来越意识到“封装工艺”的重要性。 顺应发展潮流,SK海力士为了量产基于HBM(High Bandwidth Memory,高带宽存储器)的先进封装产品和开发下一代封装技术,尽力确保生产线投资与资源。一些曾经专注于半导体存储器制造技术的企业也纷纷布局封装技术领域,其投资力度甚至超过专攻此类技术的OSAT1(外包半导体组装和测试)公司。这是因为,越来越多的企业深信封装技术将会成为半导体行业及企业未来的核心竞争力。

1 OSAT(Outsourced Semiconductor Assembly and Test, 外包半导体组装和测试):专门从事半导体封装和测试业务的公司。

本文将以易于理解的语言来阐述封装技术,帮助公众不再因为复杂难懂而对这项技术望而却步。文章将探究封装技术的意义、作用和演变过程,并探讨SK海力士封装技术的发展历程以及由此引发的当下对异构集成的关注。最后,本文也将介绍SK海力士的未来技术发展方向。

封装技术的意义和作用

首先,我们来看封装工艺的四项主要功能。第一也是最基本的,保护半导体芯片免受外部冲击或损坏。第二,将外部电源传输至芯片,以确保芯片的正常运行。第三,为芯片提供线路连接,以便执行信号输入和输出操作。第四,合理分配芯片产生的热量,以确保其稳定运行。近来,散热(Heat Dissipation)或热分配功能的重要性与日俱增。

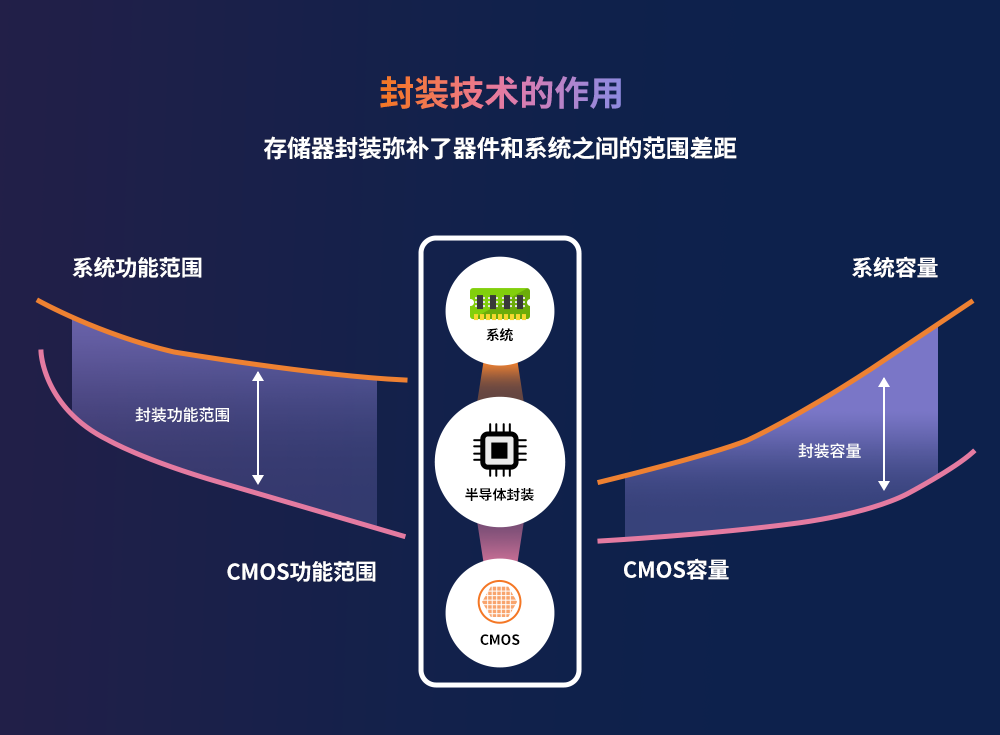

封装的作用如图1所示。例如,系统所需功能范围与CMOS2(互补金属氧化物半导体)提供的功能范围之间存在显著差距,但可通过封装技术进行弥补。同样,系统所需容量(Density)和CMOS提供的容量之间也存在差距,而这一问题也可借助封装工艺加以解决,因为封装工艺可提升密度(Density-up)从而提高CMOS的容量。换句话说,封装技术充当着半导体器件(device)与系统之间的桥梁。因此,这种连接方法变得越来越重要。

2 CMOS(Complementary Metal Oxide Semiconductor, 互补金属氧化物半导体):一种集成电路设计,应用于使用半导体技术的印刷电路板(PCB)。

图1. 存储器封装弥补了器件和系统之间的范围差距

封装技术发展的三个阶段:堆叠竞争、性能竞争、整合

封装技术的发展历程可以划分为三个主要时期。过去,一个封装中只包含一个裸片。因此,封装操作比较简单,也没有任何差异化因素,封装技术的附加价值较低。然而,到了20世纪初,随着向FBGA3(细间距球栅阵列)的转变,多芯片堆叠封装技术开始盛行。这一时期可以被称为“堆叠竞争时期”。由于可以将芯片相互堆叠,因此封装形式变得更加多样化,还根据存储器芯片的不同组合开发了各类衍生产品。MCP4(多芯片封装)也出现在这一时期,该技术可以将DRAM和NAND集成在同一封装中。

3 FBGA(Fine-pitch Ball Grid Array, 细间距球栅阵列):一种基于球栅阵列技术的集成电路表面贴装型封装(芯片载体)形式。其触点更薄,主要用于系统级芯片设计。

4 MCP(Multi Chip Package, 多芯片封装):通过在一个封装外壳内垂直堆叠两种或两种以上不同类型存储器半导体形成的产品。

第二个时期始于2010年之后,当时出现了一种利用芯片凸块(Bump)的互连(Interconnection)方法。因此,运行速度和器件属性裕度(Margin)发生了变化。这一时期可以称为“性能竞争时期”,因为在2010年之前,封装技术通常涉及金属线连接,而凸块的引入缩短了信号路径(Signal Path),提高了速度。同时,采用TSV5(硅通孔)技术的堆叠方法大幅增加了I/O(输入/输出)数量,可连接10246 个wide I/O,即使在低电压状态下也可实现高速运行。在性能竞争时期,芯片性能依据封装技术而异,这成为满足客户要求的重要因素。由于封装技术可能影响企业的成败,因此封装技术的价值持续增长。

第三也是最后一个时期始于2020年,是在先前所有封装技术的基础上发展起来的。这一时期可以被称为“整合时期”,需要借助技术将各类芯片集成到同一封装内,还需要在整合系统时将多个部分连接至同一模块。在这一时期,封装技术本身已成为一种系统解决方案,可为客户提供定制化的封装解决方案,来实现小批量生产。从这一点来说,封装技术将成为决定企业成败的关键因素。

5 TSV(Through-Silicon Via, 硅通孔):一种在DRAM芯片内钻数千个细孔并通过垂直贯通的电极将上下两层的通孔连接在一起的互联技术。

6 1,024:标准DRAM最多包含64个I/O,而HBM3最多包含1024个wide I/O。

图2. 封装技术发展带来的变化

SK海力士封装技术的发展历程

直到堆叠竞争时期,SK海力士的封装技术并未表现出显著优势;而随着性能竞争时期的到来,SK海力士的封装技术开始在市场中崭露头角。CoC(芯片内建芯片)7技术表现尤为突出,这项技术将凸块互联 (Bump Interconnection)与引线键合(Wire Bonding)相结合,在提高运行速度和降低成本方面实现了突破。如今,该技术已专门应用于SK海力士高密度模块的生产和量产。SK海力士还开发了MR-MUF(批量回流模制底部填充)8技术并将其应用于HBM产品中。通过这项技术确保了HBM 10万多个微凸块互连的优良质量。此外,该封装技术还增加了散热凸块的数量,同时由于其采用具有高导热性的模制底部填充材料,与竞争产品相比具有更加出色的散热性能。这项技术的应用巩固了SK海力士在HBM市场的地位,并使SK海力士在HBM3市场占据领先地位。

7 CoC(Chip-on-Chip, 芯片内建芯片):是指在不使用TSV(硅通孔)技术的情况下,以电气方式连接两个(或以上)die的封装技术。

8 MR-MUF(Mass Reflow Molded Underfill, 批量回流模制底部填充):将半导体芯片贴附在电路上,并在堆叠芯片时使用“EMC (Epoxy Molding Compound, 液态环氧树脂模塑料”填充芯片之间或芯片与凸块之间间隙的工艺。截至目前,NCF技术已经用于该工艺。NCF是一种在芯片之间使用薄膜进行堆叠的方法。MR-MUF与NCF相比,导热率高出两倍左右,对工艺速度和良率都有很大影响。

在如今的融合时期,SK海力士正积极发展混合键合(Hybrid Bonding)技术,这种技术采用Cu-to-Cu(铜-铜)键合9替代焊接。此外,SK海力士也在研究采用Fan-out RDL(扇出型重新分配层)技术10等各种封装技术的方案。混合键合技术可以进一步缩小间距11,同时作为一种无间隙键合(Gapless Bonding)技术,在芯片堆叠时不使用焊接凸块(Solder Bump),因此在封装高度上更具优势。此外,扇出型RDL技术适用于多个平台,SK海力士计划将该技术用于芯粒(Chiplet)12技术为基础的集成封装。线间距(Line Pitch)和多层(Multi-Layer)是扇出型技术的关键组成部分,SK海力士计划到2025年将确保1微米以下或亚微米(Sub-micron)级水平的RDL技术。

9 Cu-to-Cu(Copper-to-Copper, 铜-铜)键合:封装工艺的一种混合键合方法,可在完全不使用凸块的情况下将间距缩小至10微米及以下。当需要将封装内的die相互连接时,可在此工艺中采用铜-铜直接连接的方法。

10 RDL(Redistribution Layer, 重新分配层):集成电路上形成的额外金属布线层,旨在重新排列I/O焊盘,将焊盘重塑到所需位置,以便于在必要时操作焊盘。例如,芯片中心的凸块阵列可重新分配到靠近芯片边缘的位置。重新分配焊盘有助提高接触密度,并实现后续封装步骤。

11 间距:互连线之间中心到中心的最小距离

12 芯粒:该技术使用控制器或高速存储器等将芯片分开,并将它们作为单独晶圆进行制造,最后在封装工艺中对它们进行重新连接

图3. SK海力士最新封装技术

封装技术将成为提供整体系统解决方案的重要手段,其功能不再局限于原始的芯片保护和电源供应等功能。在不久的将来,各公司将依赖封装技术助力其成为半导体行业的领军者。几年前,东亚地区一家大型晶圆代工企业使用集成式扇出型(Integrated fan-out, InFO)封装技术建立起全新的系统级封装(System-in-Package, SiP)业务,同时扩大了晶圆代工销售业务范围。就像这家晶圆代工企业以生产控制器而闻名,SK海力士以生产HBM等高性能半导体存储器著称。SK海力士在整合时期进一步加强异构集成和扇出型RDL技术等先进封装技术。不仅作为存储器IDM(Integrated Device Manufacturer, 垂直集成制造)公司引领业界,进一步成为引领未来半导体储存器行业的“解决方案提供者(Solution Provider)”。

文章来源:SK海力士