引言:富昌电子(Future Electronics)一直致力于以专业的技术服务,为客户打造个性化的解决方案,并缩短产品设计周期。在第三代半导体的实际应用领域,富昌电子结合自身的技术积累和项目经验,落笔于SiC相关设计的系列文章。希望以此给到大家一定的设计参考,并期待与您进一步的交流。

前两篇文章我们分别探讨了SiC MOSFET的驱动电压,以及SiC器件驱动设计中的寄生导通问题。本文作为系列文章的第三篇,会从SiC MOS寄生电容损耗与传统Si MOS作比较,给出分析和计算过程,供设计工程师在选择功率开关器件时参考!

电力电子行业功率器件的不断发展,第三代半导体(SiC,GaN)代替硅半导体已经是大势所趋。

由于Si MOSFET其输入阻抗高,随着反向耐压的提高,通态电阻也急剧上升,从而限制了在高压大电流场合的应用。为了进一步提高开关电源的效率,迫切需要一种能承受足够高耐压和极快开关速度,且具有很低导通电阻和寄生电容的功率半导体器件。

SiC MOSFET有极其低的导通电阻RDS(ON),导致了极其优越的正向压降和导通损耗, 并且具有相当低的栅极电荷和非常低的漏电流,能适合超快的开关速度,更适合高电压大电流高功率密度的应用环境。

我们都知道开关电源的频率越高,每秒开关管改变状态的次数就越多,开关损耗和与开关频率成正比。

富昌电子在长期的电源电路研究中发现:开关电源中所有与开关频率有关的损耗,最显著的往往是开关管自身产生的损耗。

本文从MOSFET的寄生电容的角度,结合BOOST PFC电路对Si MOSFET和SiC MOSFET展开讨论。

对于功率MOSFET寄生电容,在开关转换的阶段,MOSFET栅极表现为一个简单的输入电容。通过驱动电阻 充电或放电。实际上,栅极对漏极和原极之间发生的事情“漠不关心”。功率MOSFET可等效为下图:

从驱动信号角度去观察栅极,有效输入充电电容Cg是Cgs与Cgd并联:

因此,栅极电容充放电循环的时间常数为:

从这个公式来看,似乎暗示着MOSFET导通和关断时的驱动电阻是一样,实际上两者有比较大的差别,那是因为,我们希望导通时的速率稍慢,而关断时的速率稍快的原因。

MOSFET的寄生电容在交流系统中的表示方法为:有效输入电容Ciss,输出电容Coss,反向传输电容Crss. 它们都与MOSFET寄生电容有关:

通常也会写成:

为了在同条件下比较Si MOSFET 和 SiC MOSFET的寄生结电容对高频电源效率的影响。我们用全电压输入,输出500w,工作频率75kHz的PFC电路来做比较,选择onsemi, SI MOSFET FQA6N90C 和 SiC MOSFET NTHL060N090SC1来完成该对比。

富昌电子在研究过程中了解到,输出功率达到500W,Si MOSFET 需要两个MOS 并联才能满足设计要求,本文中我们暂且忽略这个差别,先从单个的SI MOSFET和SiC MOSFET来做比较。

静态寄生参数对比:

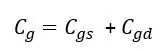

FQA6N90C (SI MOSFET)

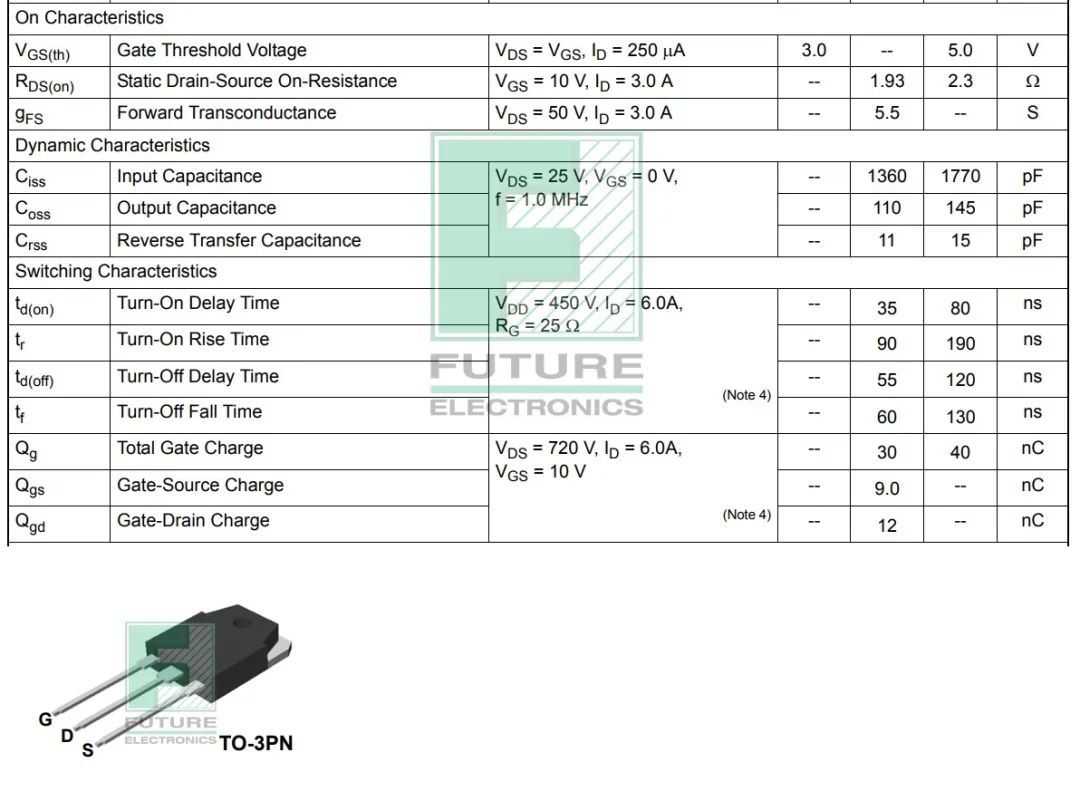

NTHL060N090SC1(SiC MOSFET):

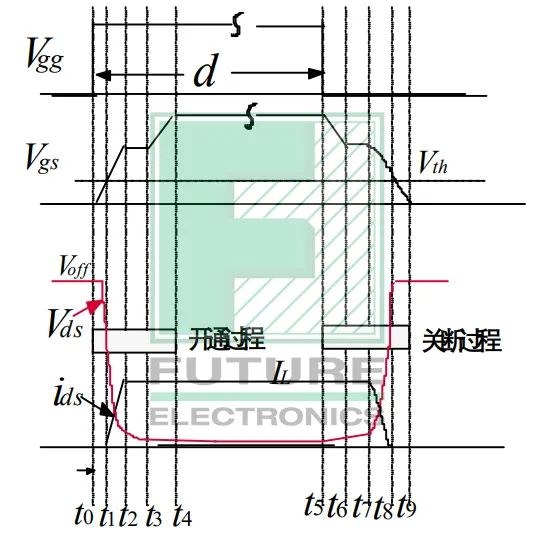

在实际MOSFET 工作过程中的电压和电流波形如下:

MOSFET的导通过程中的驱动损耗在 t1+ t2+ t3 +t4时间内产生,而交叉时间仅为:t2+ t3,关断过程中的驱动损耗在 t6+ t7+ t8 +t9时间内产生,而交叉时间仅为:t7+ t8 。

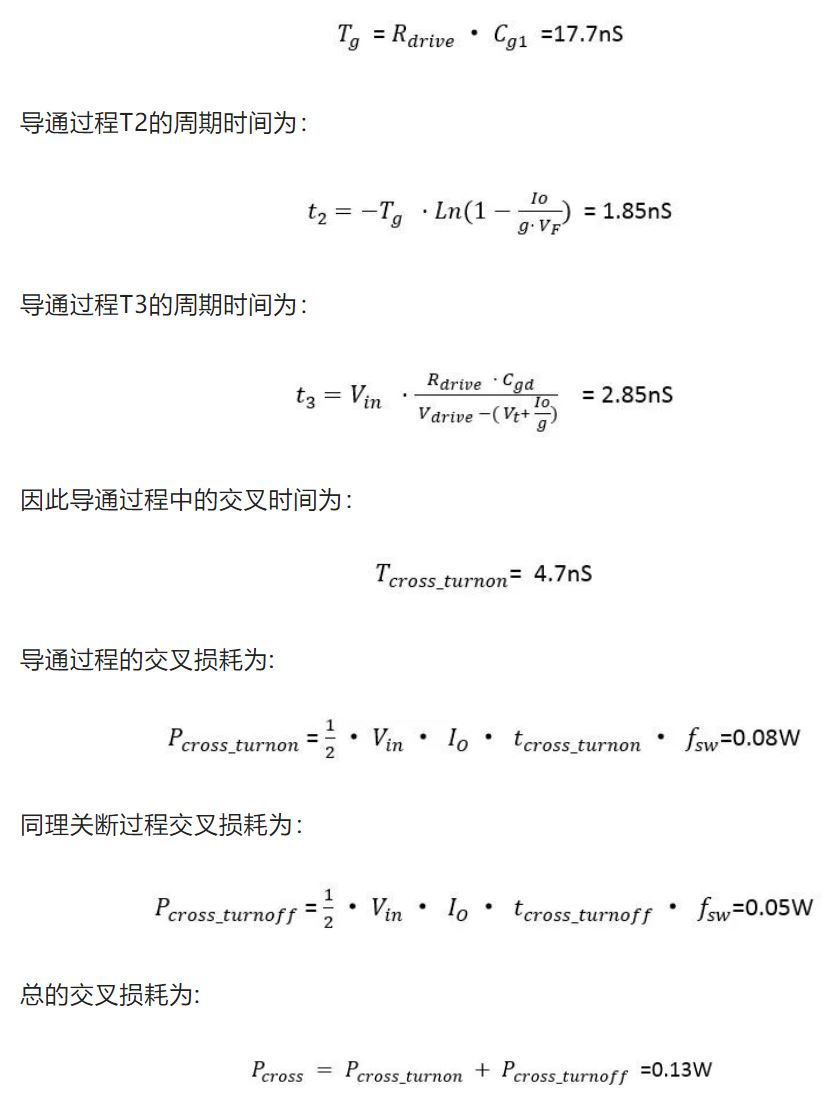

假设MOSFET门极的驱动电阻为10欧姆,关断电阻为5欧姆,可得FQA6N90C时间常数Tg:

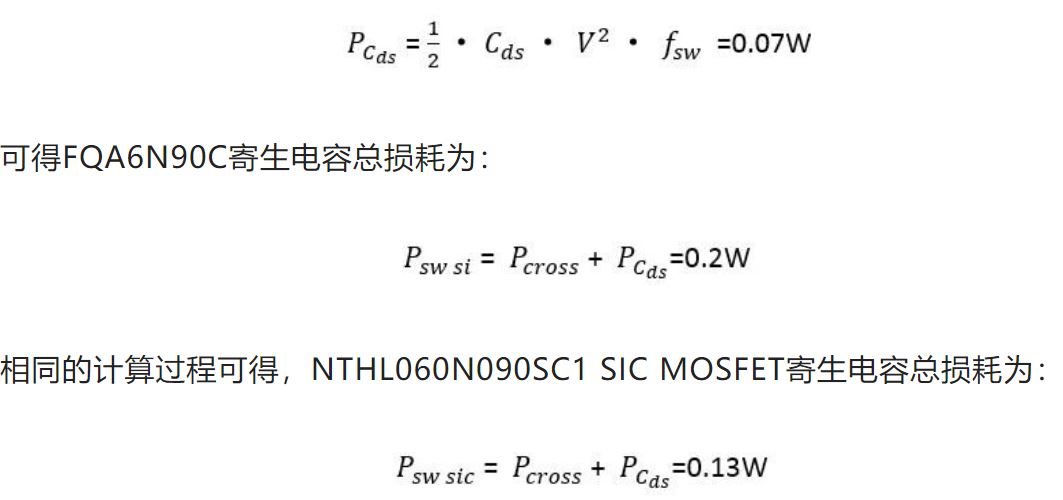

寄生电容C_ds,因为它不和栅极相连,因此不影响到MOSFET导通过程中的V-I交叉损耗。但是,该电容在MOSFET关断时充电,在MOSFET导通时把储能全部倾泻到MOSFET中。因此在计算MOSFET的损耗时,该电容不能忽略,特别在离线式的AC-DC的电源中,该寄生电容严重影响到电源的效率。在低压输入的电源中,该电容对效率的影响表现的不是很明显。

富昌电子研究结论:在同样输入和输出的电参数,封装几乎相同的条件下,比较Si Mosfet和SiC Mosfet寄生电容带来的损耗可知,SiC节省了60%的寄生损耗。如果采取两颗Si MOFET并联,达到输出500W PFC的设计目的,Si MOFET寄生电容的损耗是SiC的3.07倍。

总结

本文针对MOS的寄生电容做出了分析,并选用onsemi同等功率的SiC与SiMOST进行了设计比较。这部分的损耗,只是电路实际工作过程中MOSFET损耗的一部分,MOSFET的损耗分析稍显复杂, 此处没有展开探讨,富昌电子后续会连载文章,剖析电路设计中的难点。敬请期待!