从国产 4×112G ASP 流片,看数据中心互连的技术分叉

作者:电子创新网编辑部

在 AI 算力持续扩张、800G 光模块加速落地的背景下,高速互连正在从“性能竞赛”阶段,进入一个更现实的问题周期:功耗、延迟与系统复杂度,开始与带宽本身同等重要。

长期以来,oDSP(光学数字信号处理器)几乎被视为高速光互连的“标准答案”。但近期,随着国内模拟芯片公司 米硅科技 完成 4×112G ASP(Analog Signal Processor)收发套片 的首次流片并通过核心验证,一个被忽视的问题重新浮出水面:

在大量短距、高密度、强算力内部互连场景中,

我们是否真的需要一套“为最复杂信道而生”的 DSP 架构?

这并不是一次简单的国产替代故事,而是一次关于 高速互连技术路线正在发生分化 的信号。

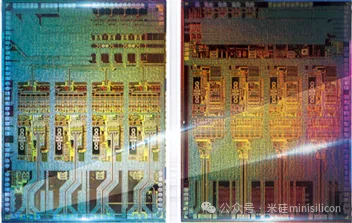

图:米硅科技4×112G 模拟ASP (CDR) 收发套片

一、oDSP 为何强大,又为何开始“显得沉重”

oDSP 的成功,源于它对不确定性的强大包容能力。

通过 ADC 将模拟信号数字化,再借助复杂 DSP 算法完成均衡、补偿与纠错,oDSP 能在 长距离、复杂信道、PAM4 调制条件 下维持稳定通信。这使其在 400G/800G 光模块时代,迅速成为主流方案。

但这一能力并非没有代价:

功耗持续攀升,单颗 112G oDSP 通常达到 8–12W

数字流水线引入微秒级系统延迟

芯片成本与 PCB 复杂度显著提高

高端产品高度依赖海外供应体系

在跨机房、跨数据中心场景中,这些代价仍然是“必要成本”;

但在 AI 服务器机柜内部、GPU 节点之间、AEC/DAC 等短距互连 中,这种设计开始显得“性能过剩”。

二、模拟 ASP 的核心逻辑:把问题解决在信号还“年轻”的时候

米硅科技选择的,并不是“轻量版 DSP”,而是彻底绕开数字路径。

其 ms89040 + ms88040 套片,通过高度集成的 模拟 CDR + Driver / TIA,在模拟域内完成时钟恢复与信号重整,不引入 ADC、DSP 与系统级 FEC。

这背后的工程哲学非常清晰:

与其在信号严重退化后,用算法“强行修复”,

不如在信号刚产生和传输的阶段,就把抖动与时序稳住。

在 112G PAM4 速率下实现这一点,对模拟设计提出了极高要求:

PLL 相位噪声、环路稳定性、抖动容限、工艺与温度一致性,都是“硬门槛”。

这也是为什么,模拟 CDR 在如此高数据率下,反而成为稀缺能力。

三、技术路线正在分叉,而非简单替代

如果将视角从“产品对比”拉升到“技术路线”,会发现高速互连并不存在单一路径,而是已经形成了清晰分工。

国内外主流高速互连技术路线对比(112G PAM4 及以上)

技术路线 | 代表厂商 / 方案 | 核心处理方式 | 主要优势 | 主要代价 / 局限 | 典型适用场景 |

数字 oDSP 路线 | Marvell、Broadcom | ADC + DSP 算法 | 支持复杂信道 | 功耗高、延迟大、成本高 | 长距光模块 |

国产 oDSP 路线 | 国内 DSP 初创企业 | ADC + DSP | 战略自主可控 | 制程与验证周期长 | 中长期国产替代 |

Retimer / Smart Retimer | Semtech 等 | CDR + 均衡 | 延迟与功耗介于 DSP 与模拟之间 | 集成度有限 | AEC / 板级互连 |

ASP + 模拟 CDR | 米硅科技 | 纯模拟 CDR + Driver/TIA | 低功耗、低延迟、结构简化 | 不适合长距复杂信道 | 机柜内互连<br>短距光模块 |

LPO / 线性直驱 | 多厂商探索 | 线性放大 | 极低功耗、极低延迟 | 工程难度高 | 极短距互连 |

这张表本身揭示了一个关键事实:

米硅的 ASP 方案,并不是“挑战 DSP 主战场”,而是精准卡位一个 DSP 并不擅长、但需求正在快速增长的细分空间。

四、真正的独特观点:高速互连的“系统重心”正在下沉

这也是本文最重要的判断:

高速互连的技术重心,正在从“跨得更远”,转向“连得更密、更省、更快”。

AI 服务器的互连特征,与传统电信网络完全不同:

距离更短(米级到百米级)

连接密度极高

延迟直接影响算力效率

功耗与散热成为系统级瓶颈

在这样的系统假设下,oDSP 并非错误,而是“为另一类问题而设计”。

而 ASP + CDR,则恰好踩在 AI 集群内部互连的工程真实需求上。

这也是为什么,模拟路径在经历多年“被低估”之后,重新获得产业关注。

五、从 112G 到更高:模拟路线的意义不止于“替代”

据公开信息,米硅科技已启动 4×224G ASP(CDR) 的研发规划。

这意味着,其目标并不仅是解决当下的 112G,而是在 更高速率短距互连 中提前占位。

需要强调的是,这并不意味着模拟路线会“全面取代 DSP”。

更现实的判断是:

DSP 继续统治长距、相干与复杂信道

ASP / Retimer / LPO 覆盖短距、高密度、低延迟互连

系统架构将首次真正“按场景选路线”,而非“一刀切”

结语:不是颠覆,而是一次迟到的分工回归

米硅 4×112G ASP 的意义,不在于制造“全球第一”的口号,而在于它用一颗可工作的芯片,证明了一件事:

在高速互连这件事上,

数字并非唯一答案,模拟也并未过时。

当产业开始正视功耗、延迟与系统复杂度的真实成本时,

这条“模拟路径”,很可能会成为 AI 时代互连架构中不可或缺的一部分。

* 本文为原创文章,转载需注明作者、出处及原文链接,否则,本网站将保留追究其法律责任的权利。