欢迎来到 “掌握 PCB 设计中的 EMI 控制” 系列的第四篇文章。在本文中,我们将探讨电磁干扰(EMI)管理的高级要点,这些要点对高效 PCB 设计至关重要。

设计印刷电路板(PCB)时,核心挑战之一是确保设计通过辐射和传导发射测试。这不仅是满足法规标准的关键,也能确保 PCB 在目标环境中正常运行,避免对其他设备和系统产生干扰。

同样重要的是实现对外部和内部发射的抗扰性,这有助于确保最终产品的可靠性和性能。

设计抗 EMI 的 PCB 时,需明确一个关键概念:辐射主要由电路中的电流变化而非电压引起。这意味着所有电路都会因固有电流变化而不可避免地产生一定程度的电磁辐射,设计师的核心挑战在于管理和控制辐射强度。

为实现更好的电磁兼容性(EMC),我们需聚焦于设计能有效约束和最小化电磁辐射的 PCB,这涉及处理两种主要辐射类型:

差模电流辐射;

共模电流辐射。

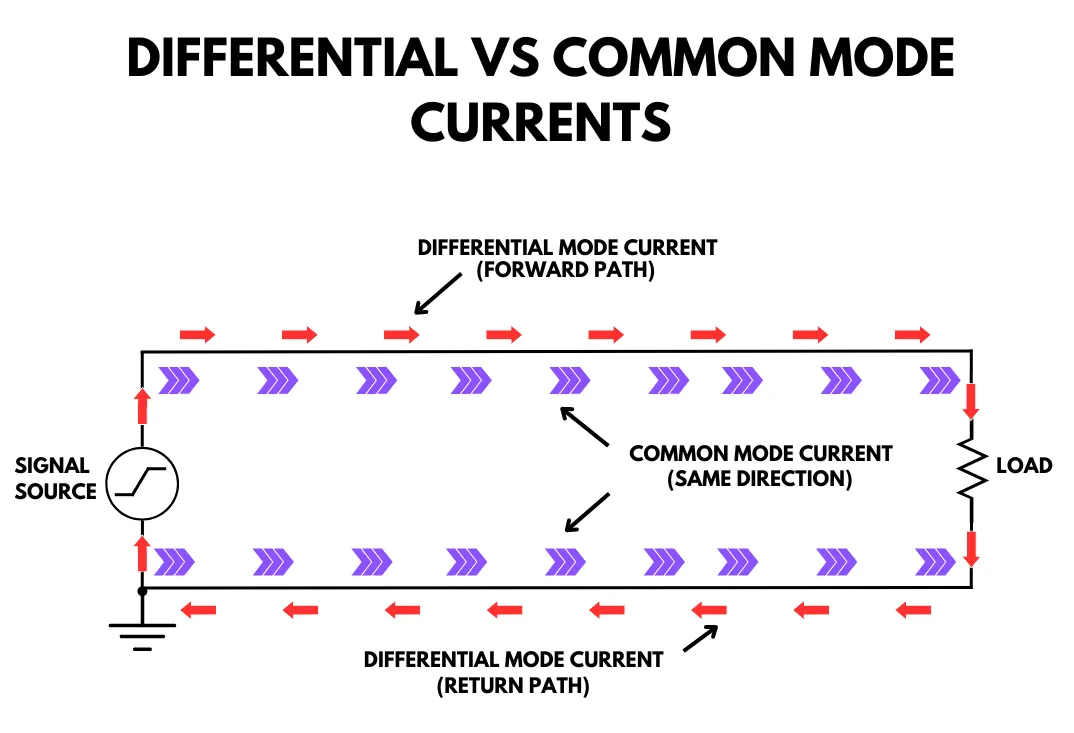

图 2:电路中的差模与共模电流(共模电流返回路径未显示)。参考:Dario Fresu

简单来说,差模电流可视为通过不同路径 “反向流动” 的电流,而共模电流则是沿电路路径以相同 “公共” 方向流动的电流。

如何最小化差模电流辐射

差模电流是电路正常运行的基础,它们在集成电路(IC)和元件之间流动,是 PCB 电路设计的一部分。

差模电流沿电路布局形成的环路流动,环路面积直接影响辐射水平:环路面积越大,辐射越强,且频率越高,辐射也越显著。

降低差模辐射的策略包括:

1. 减少走线中的电流;

2. 降低电流频率;

3. 最小化电流环路面积。

然而,减少电流或降低频率(策略 1 和 2)通常不切实际,因为可能显著影响电路效率。最具实操性的方法是最小化电流环路面积,这也是 PCB 设计师可直接控制的关键因素。

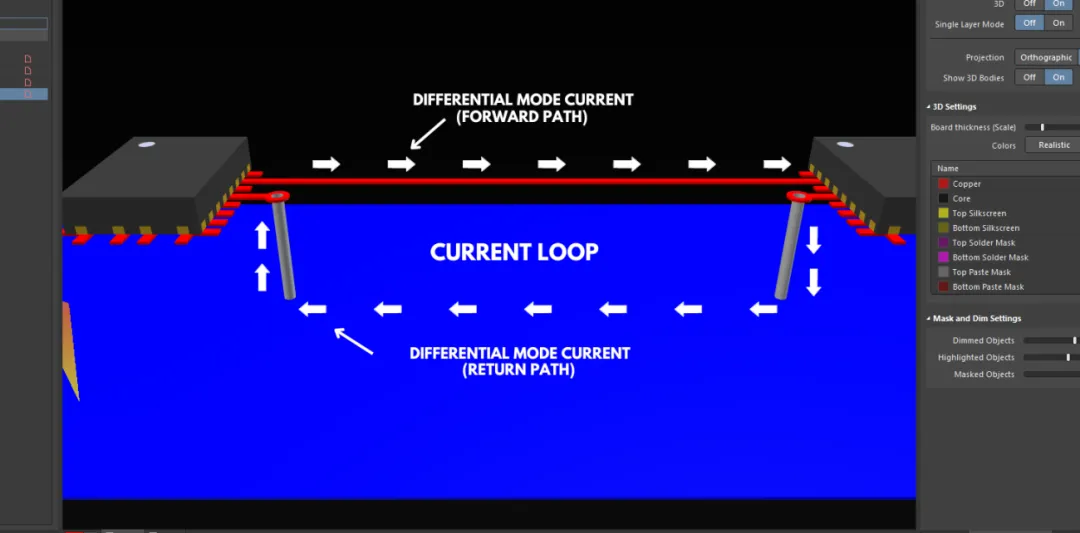

一种高效方法是在叠层结构中为信号走线配置紧邻的返回参考平面,这可使正向和返回电流形成的环路面积极小化,从而抑制辐射。结合尽可能缩短信号走线的设计,能最大限度降低差模电流辐射。

当然,元件布局、减少信号串扰以及管理可能将噪声传递到附近电缆的耦合机制,对减少辐射也很重要,但这些均属于次要因素,核心仍是最小化电流环路面积。

这一技术直接针对差模电流辐射的根源,效果尤为显著。

如何最小化共模电流辐射

设计师需关注的另一类重要电流是共模电流。与有意设计的差模电流不同,共模电流并非原理图中的显式设计元素,它们并非电路运行必需,主要源于设计中的寄生效应。

识别和控制这些寄生电流颇具挑战性,因为其来源往往并不明显。共模电流通常在差模电流流经电路中的寄生元件时产生。

这些寄生效应尤其存在于返回参考导体(通常称为 “地” 或 “信号地” 导体)中。返回参考导体中出现寄生效应的问题,主要是因为在实际情况中,元件和导体并非完美无缺,与理想状态相去甚远。

例如,电路中的铜质走线不仅具有电阻,还表现出电感和电容特性,且这些寄生参数随信号频率升高而显著影响电路。

与主要受环路面积影响的差模辐射不同,共模电流主要受导体长度和噪声频率影响(导体长度的影响在超过一定阈值后趋于稳定,本文暂不深入探讨)。

对于电长度较短的电缆,共模电流辐射可建模为偶极子(或单极子)天线发射,而非环路天线发射,这一建模差异影响辐射的产生与控制方式。

从源头有效降低共模电流辐射的策略包括:

减少共模电流;

降低共模电流频率;

最小化导致共模辐射的导体长度。

关键策略是缩短信号走线长度。尽管受系统限制无法缩短所有导体,但设计师应尽可能在可行范围内减小走线长度,这对抑制 PCB 辐射(尤其是在信号频率持续升高的趋势下)至关重要。

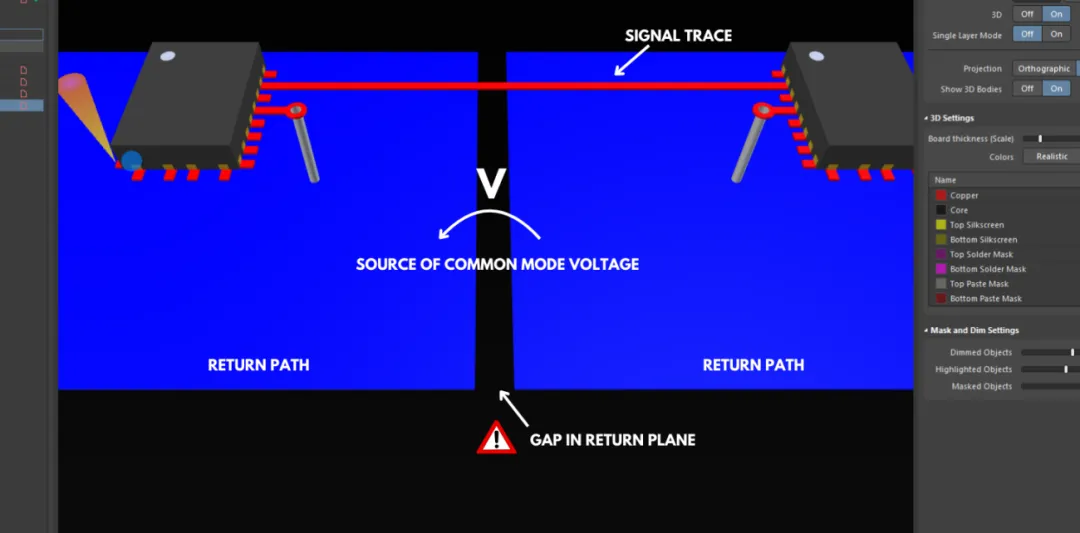

使用实心铜平面作为返回和参考平面是另一有效技术,可降低返回电流路径的电感,从而减少驱动共模辐射的电压源。

完整的铜平面(无分割或切口)通过为返回电流提供低阻抗路径,有助于维持信号完整性并降低 EMI。

如何通过缝合过孔最小化辐射

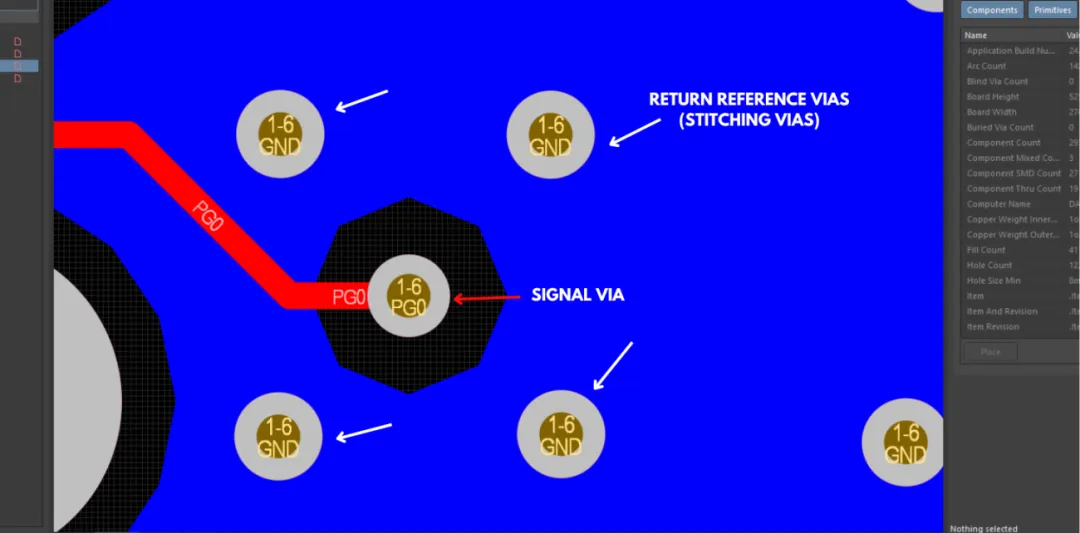

在具有多个返回参考平面的多层叠层结构中,缝合过孔是减少共模辐射的推荐技术。缝合过孔连接不同的返回参考层,确保其保持相同电位,从而减少驱动偶极子(或单极子)天线模式辐射的共模电压源,显著降低杂散噪声和 EMI。

图 5:Altium Designer® 中的缝合过孔示例

除减少共模辐射外,缝合过孔还为叠层中跨层传输的信号提供可靠的电流返回路径和参考电位,防止平面间产生辐射 —— 这类辐射不仅影响 EMI,还会损害信号完整性和 PCB 整体性能。

结论

Altium Designer® 可无缝集成到设计工作流程中,提供充分发挥专业能力所需的灵活性和先进功能,让高效 EMI 控制策略的落地更加轻松。

在下一篇文章中,我们将探讨电源分配网络(PDN)的去耦策略,为设计实践提供更多洞见。

文章来源:Altium