本文要点:

了解 EMI 与 EMC 之间的区别。

采用低功耗器件、隔离技术、PCB 防护以及热管理,减少 EMI 来源。

借助约束管理、信号完整性分析和实时 DRC 更新等工具,创建 EMI 优化设计。

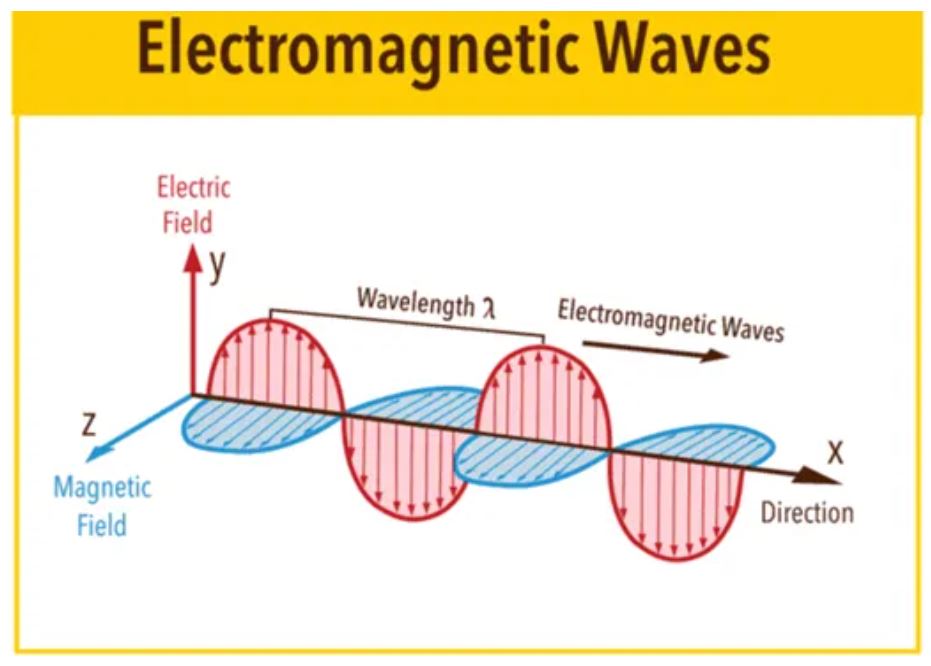

所有电子电路板都用于实现甚至增强电子流动,从而达成特定的性能目标。电流沿闭合路径流动,会产生一个向外扩展并垂直于电流方向的磁场。当该磁场附近有电子元件或信号路径时,就会发生电磁干扰(EMI,Electromagnetic Interference)。

许多 PCBA 设计首先要考虑的便是如何控制 EMI,尤其是高速电路板。对于带有辐射器分类器件的电路板,常见的方法是采用 EMI 滤波器设计。虽然滤波器效果显著,但电路板设计师还应掌握更多 PCB 设计方法,这些都是降低 EMI 的重要工具,常常需要灵活运用。

电磁干扰的构成

EMC 与 EMI:有什么区别?

大多数 PCBA 并非产品中唯一的电子或电气设备。因此,在深入探讨单板 EMI 问题之前,最好先从宏观或系统层面了解 EMI 问题。

正如电磁能量会从单个器件、导体或走线中散发出去,电路板本身也可能向外环境中释放电磁波;如果将高斯计放在 PCB 附近,就能测量到相关数值。当多块电路板紧密相邻时,实现电磁兼容性(EMC,Electromagnetic Compatibility) 就显得尤为重要。

EMC 旨在确保器件之间的 EMI 最小化,从而确保设备的正常运行。虽然 EMI 无法完全消除,但可以实现 EMC。EMI 通常指单块 PCBA 上的干扰,降低 EMI 有助于提高电路板周围环境的 EMC 水平。

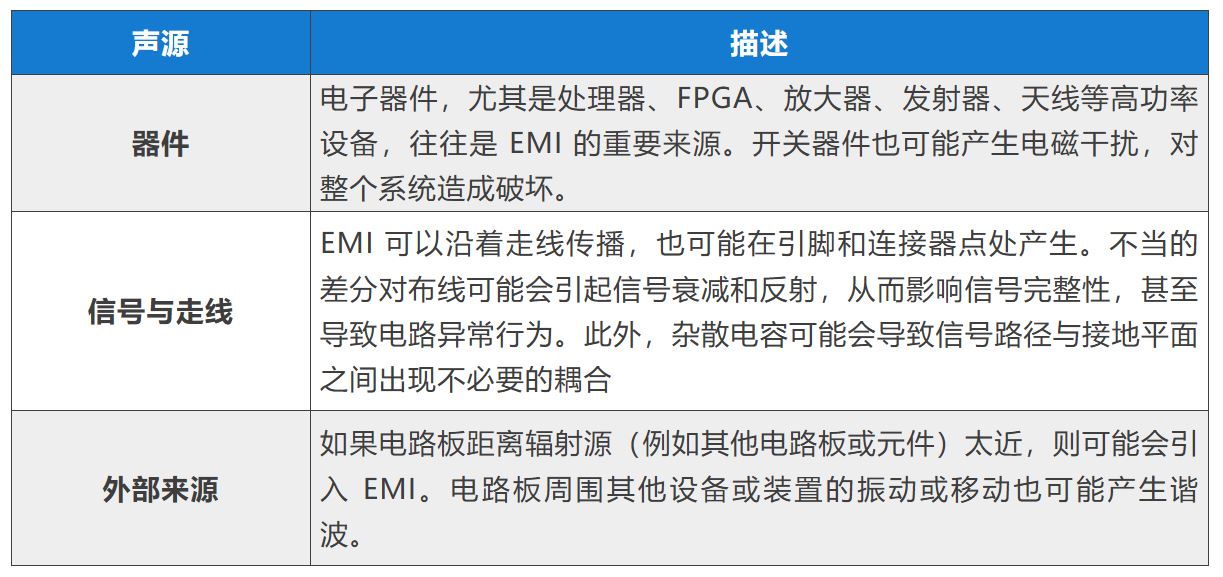

EMI 来源分类

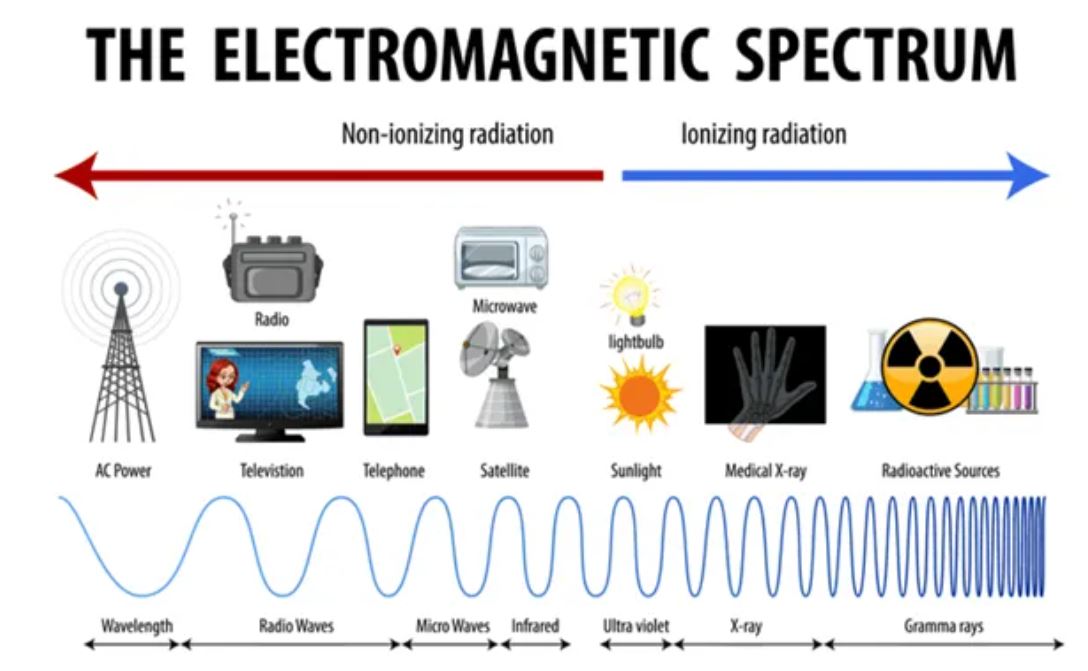

电磁覆盖无限的频率范围,几乎无处不在。如下图所示,我们日常使用的许多工具、电器和产品都会产生电磁辐射。

电磁波谱

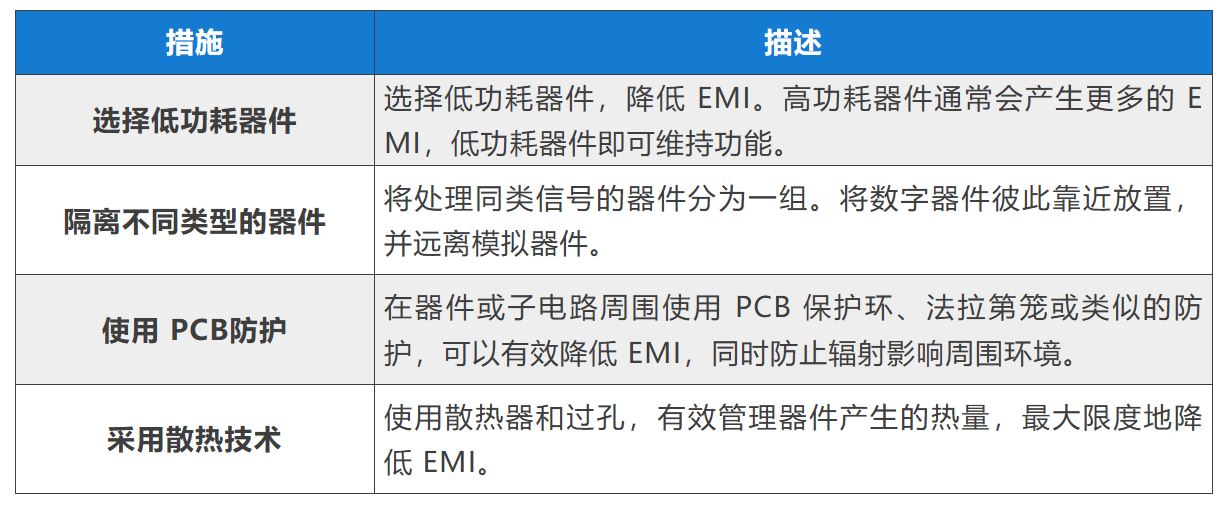

如何降低 PCB 器件的 EMI?

如前所述,器件往往是电磁辐射的主要来源,不仅会影响电路板操作,还可能干扰外部 PCBA 和电子电路。因此,为有效降低 EMI,制定减轻其负面影响的措施至关重要,如下所述。

EMC 与 EMI:有什么区别?

EMI 最小化的 PCB layout 设计

在电路板布局过程中,间距是重要考量因素之一,包括确保导电元件之间有足够的间隙和爬电距离。

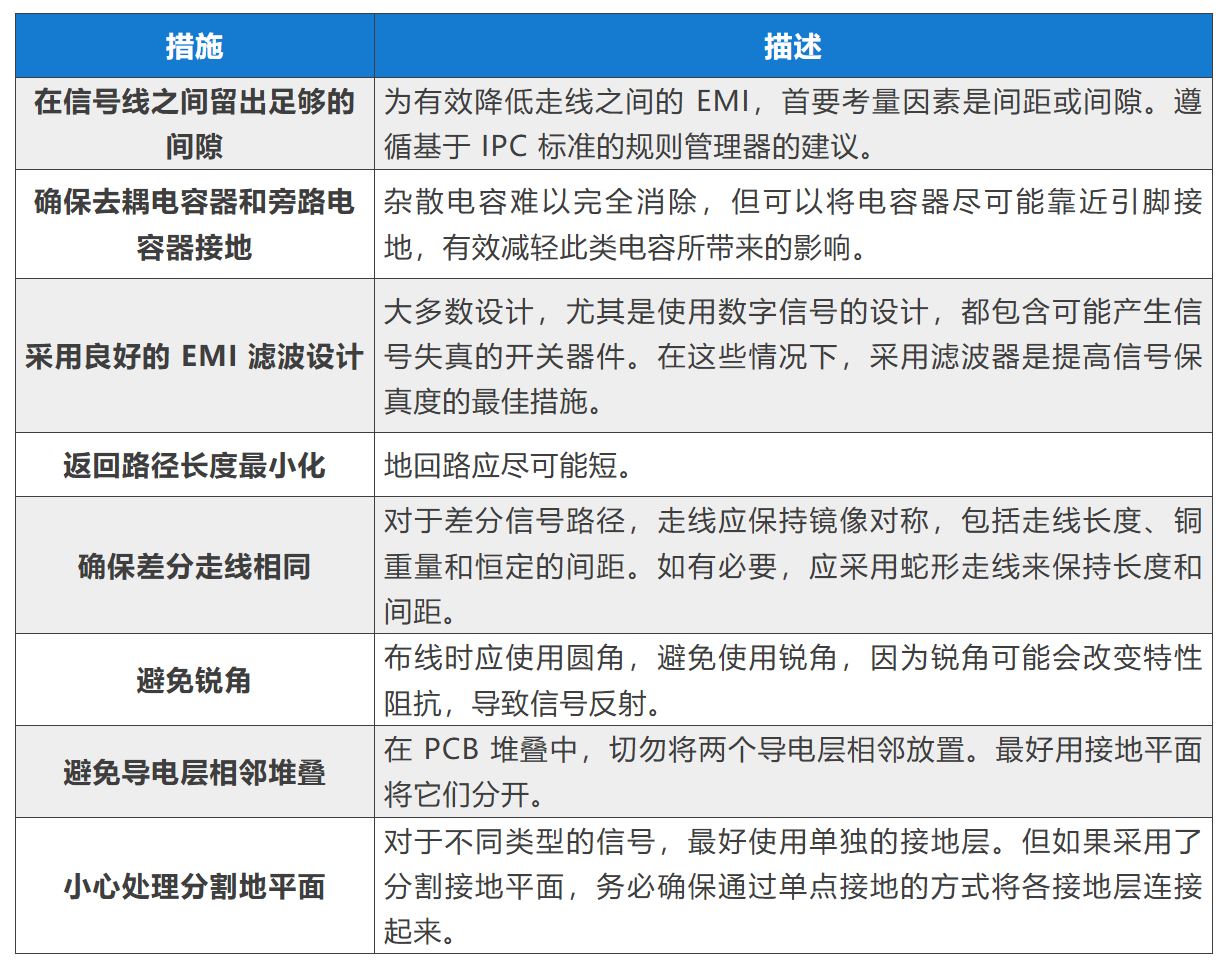

对于多层电路板而言,导电平面与接地平面之间的层叠顺序和距离也很重要,如下表所示。

如何降低来自信号和平面的 EMI

PCB layout(包括器叠层结构)有助于确保良好的信号完整性和降低 EMI。然而,任何旨在降低 EMI 的 PCB 设计指南,如果不涉及外部 EMI 的抑制措施,都是不完整的。

避免外部 EMI

最大限度地减少外部 EMI对于电路板上的信号完整性和电路运行非常重要,并且有助于 PCBA 安装环境的 EMC。以下是可以采取的措施。

如何降低外部来源的 EMI

使用屏蔽装置:屏蔽装置通常用于覆盖特定的器件或子电路。与围栏不同,屏蔽装置通常由绝缘材料制成,放置在器件顶部或将其完全封闭。

使用外壳:外壳通常被视为安全装置。然而,外壳也能有效保护电路板免受碎屑和外部 EMI 的影响。

以上关于器件、layout 和外部来源的 PCB 设计指南,均有助于降低电路板上的 EMI,并改善电路板运行环境的 EMC。此外,要高效地实施这些设计指南,往往需要借助专门的设计工具。点击下图查看白皮书,了解 Cadence 提出的自动化仿真工作流程,并且能够高效地创建 EM 仿真设计,来实现快速上市的产品开发过程。

文章来源:Cadence