三态逻辑作为一种数字电子技术中的逻辑类型,允许信号线在三种状态之间切换。本文介绍了三态逻辑电路原理并介绍了四种基本类型的三态缓冲器。如果你对三态逻辑感兴趣,相信这篇内容会让你对其有基础的认识。

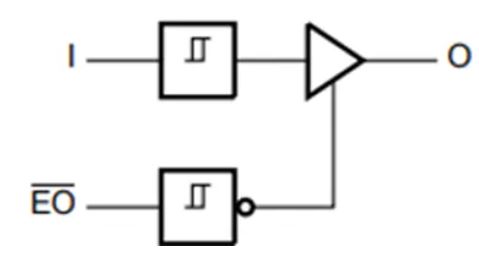

三态逻辑输入/输出

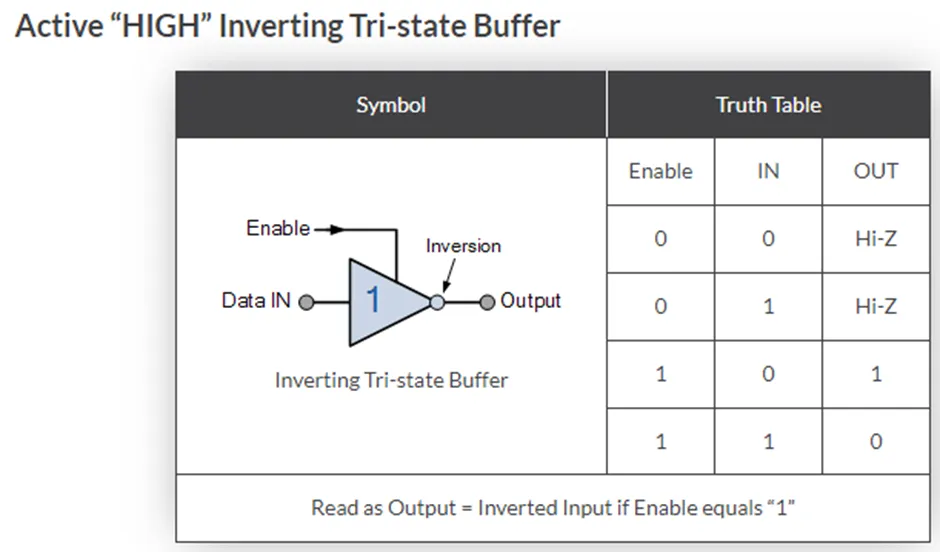

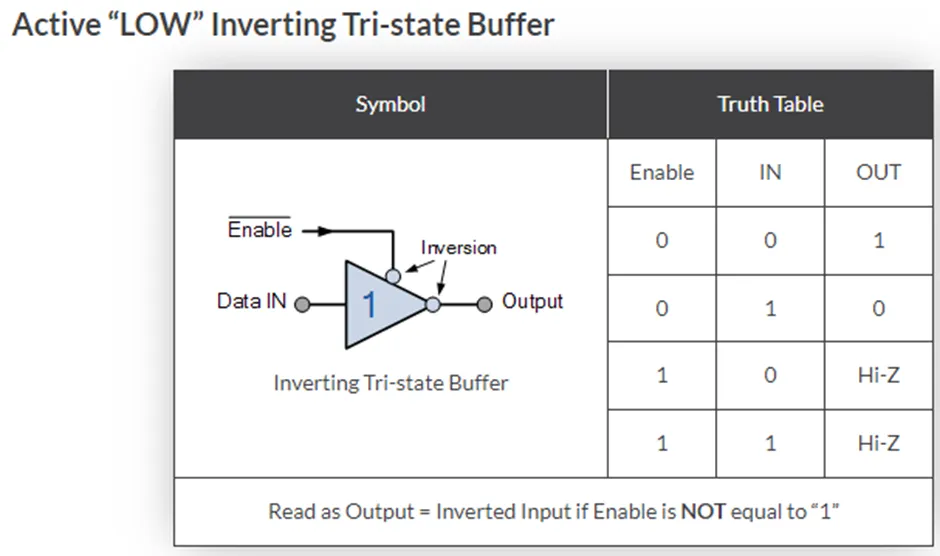

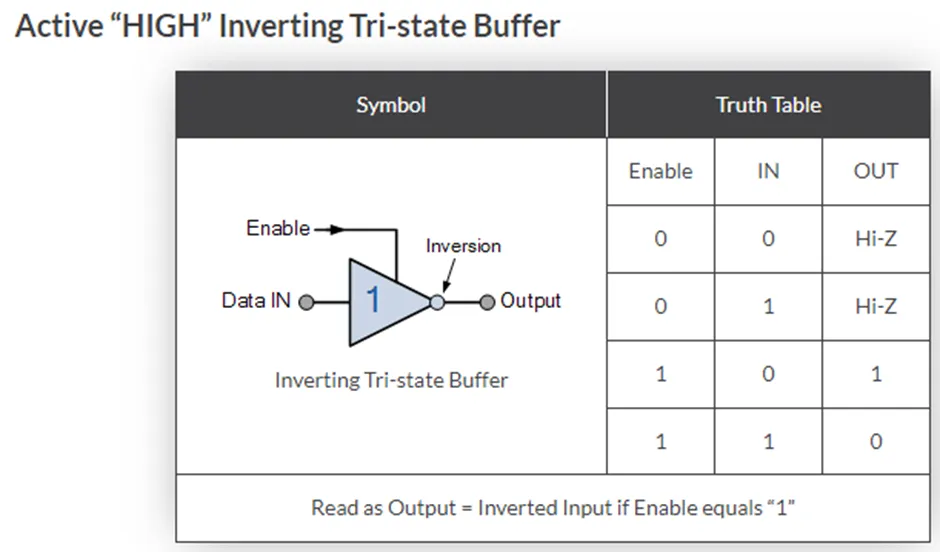

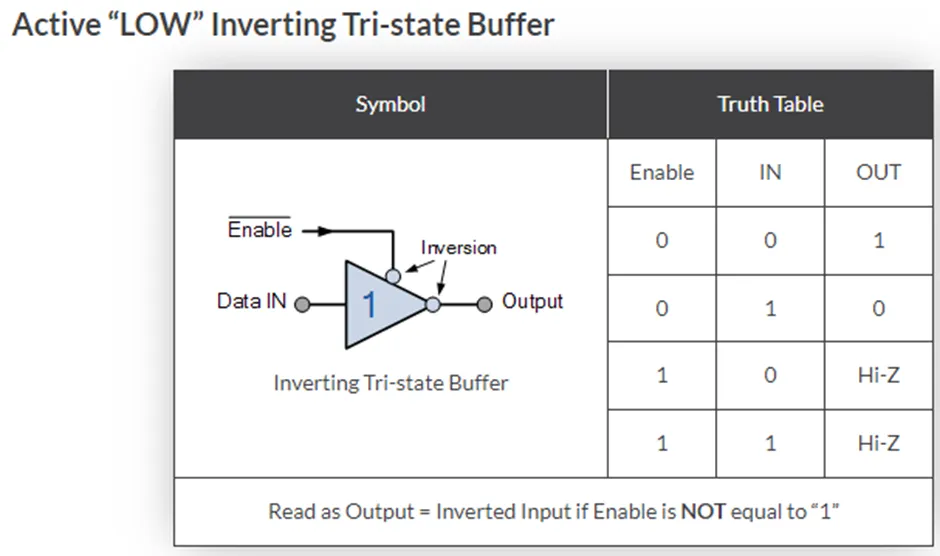

在数字电子技术中,三态逻辑(TRIS)允许输入或输出假设为1、0或 高阻抗状态 (开路)。

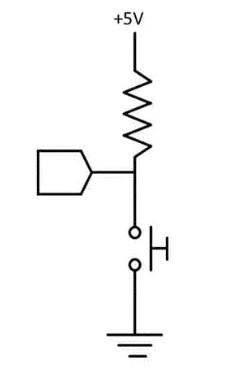

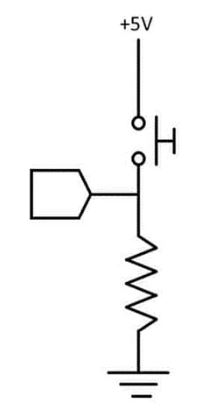

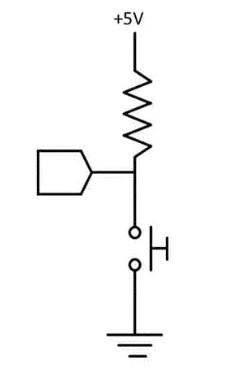

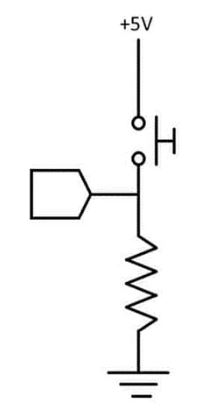

上拉电阻

文章来源:DigiKey得捷

三态逻辑作为一种数字电子技术中的逻辑类型,允许信号线在三种状态之间切换。本文介绍了三态逻辑电路原理并介绍了四种基本类型的三态缓冲器。如果你对三态逻辑感兴趣,相信这篇内容会让你对其有基础的认识。

三态逻辑输入/输出

在数字电子技术中,三态逻辑(TRIS)允许输入或输出假设为1、0或 高阻抗状态 (开路)。

上拉电阻

文章来源:DigiKey得捷