作者:电子创新网编辑部

在 AI 数据中心迅猛扩张与移动计算持续升级的双重压力下,存储厂商正站在一个关键十字路口:既要满足超大规模数据中心的算力吞吐需求,也要兼顾智能手机、边缘设备等对低功耗的严苛要求。

低功耗 DDR(LPDDR)最初为移动设备而生,但随着 AI 工作负载爆发式增长,新一代 LPDDR6 的设计理念已经同时面向“便携终端 + AI 数据中心”双场景。

在 2026 年国际固态电路会议(ISSCC 2026)上,SK 海力士发布论文,系统介绍其 LPDDR6 SDRAM 的研发成果。公司表示,其基于 JEDEC 标准的 LPDDR6 实现:

功耗降低 20%

带宽提升 50%

同时增强可靠性

LPDDR6:更高带宽、更低功耗

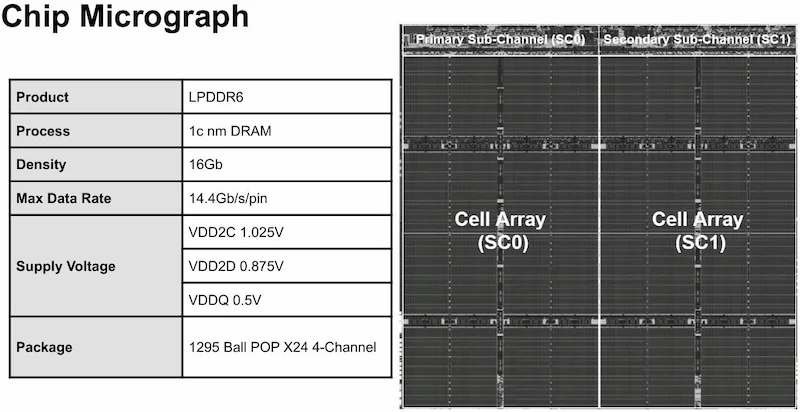

SK 海力士展示的是一颗基于 1c nm 工艺打造的 16Gb LPDDR6 器件,工作电压 1.025V,单 pin 数据速率达到 14.4Gb/s。

论文指出,其性能提升主要来自一系列架构优化,包括:

可选择性关闭未使用电路模块

提升时序协调能力

优化内部操作调度效率

通过实际硅片测试(hard silicon validation),SK 海力士验证了 LPDDR6 标准在性能与能效方面的承诺。

相较于 LPDDR5 / 5X,LPDDR6 的关键指标提升如下:

指标 | LPDDR5 | LPDDR5X | LPDDR6 |

时钟频率 | 800 MHz | 1066.5 MHz | 2677 MHz |

时钟比(CK:WCK) | 2:1 ~ 4:1 | 2:1 ~ 4:1 | 固定 2:1 |

单 pin 带宽 | 6400 Mbps | 9600 Mbps | 10667 Mbps |

工作电压 | 1.1V | 1.1V | 1.025V / 0.875V |

可以看到,在频率与带宽大幅提升的同时,电压进一步下降。

五项关键技术创新

为实现这些性能与能效突破,LPDDR6 引入了多项架构革新。SK 海力士在 ISSCC 论文中重点验证了以下五项技术。

1. Efficiency Mode(效率模式)

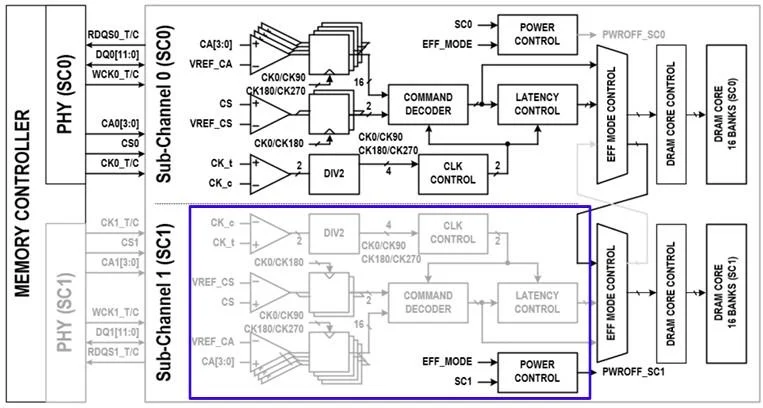

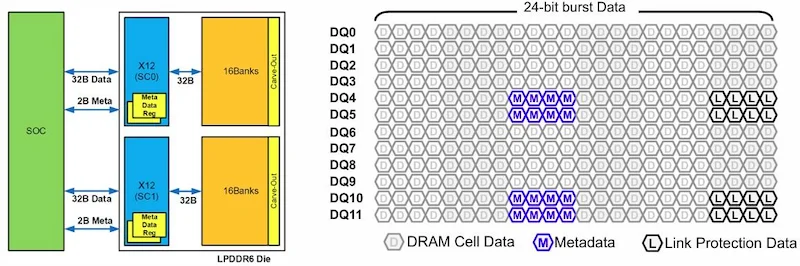

LPDDR6 采用“双子通道(dual-subchannel)架构”。每个 die 内含两个子通道,每个子通道为 12-bit 数据总线,总计 24-bit,但逻辑上仍保持 32-bit 数据传输。

这一架构带来的优势是:

正常模式下可并行运行,提升性能

效率模式下可关闭一个子通道(SC1),降低功耗

此外,在交错访问模式下,关键时钟驱动电路(命令解码、时钟控制、延迟控制等)集中在主子通道 SC0,从而减少功耗开销。

本质上,这是一个“性能 / 功耗可切换”的架构设计。

2. 基于 LDO 的 WCK 时钟树

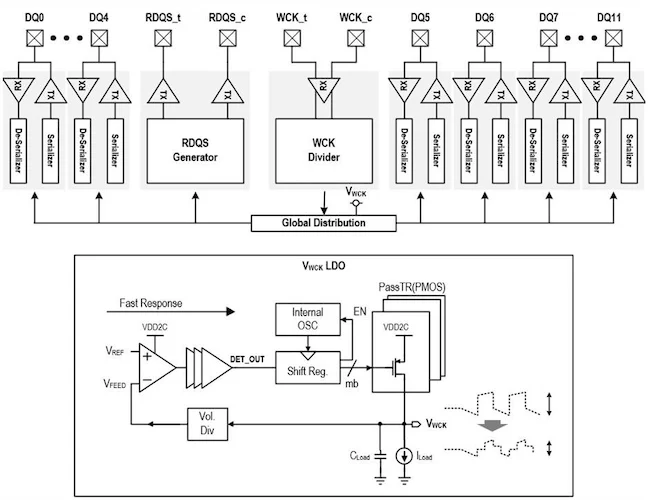

LPDDR6 引入公共写时钟(WCK)LDO 低压差稳压器设计,相较 LPDDR5:

WCK 抖动降低 30%

具体优化包括:

降低放大器增益

提高 DET_OUT(电平检测放大器)带宽

缩短响应时间

加快 WCK 开关响应

此外,通过多位寄存器同步机制,保持 WCK 与振荡器输出一致。

第三项改进通过事件驱动内部振荡器与移位寄存器响应机制,避免电压过冲问题。

这部分核心在于:高速条件下,时钟完整性成为系统瓶颈,而 LPDDR6 针对 WCK 进行了系统级优化。

3. Dynamic Write NT-ODT(动态写入非目标终端匹配)

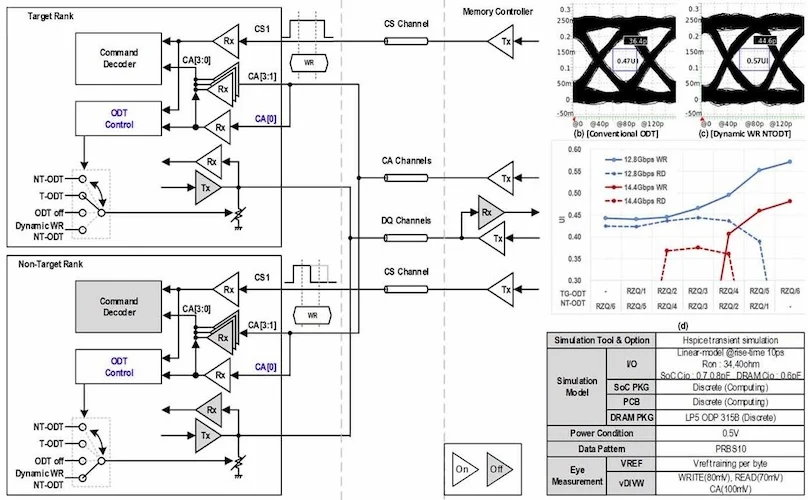

NT-ODT(Non-Target On-Die Termination)允许根据实际运行状态动态调节 ODT。

技术实现包括:

独立 ODT 控制模块

使用预定义 CS(Chip Select)模式替代传统命令解码

改进 CA 缓冲与控制逻辑

效果:

提升 DQ 数据总线信号完整性

降低功耗

这是一种兼顾 SI 与能效的终端匹配策略。

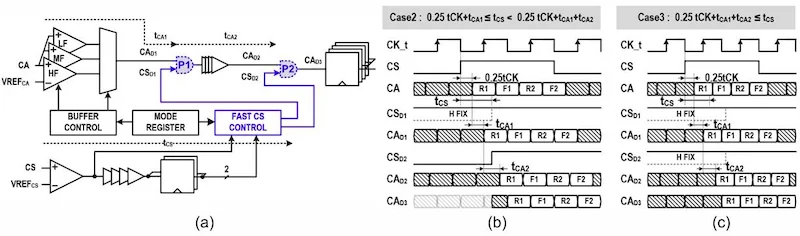

4. Fast CS Control(快速片选控制)

在多 rank 结构中,CA 与 CS 共享。传统结构下:

CS 比 CA 提前约 25% 时钟周期有效

需要额外建立 / 保持时间调整

LPDDR6 将 CS 电路划分为三个频段,并增加快速 CS 控制逻辑:

使用首个接收的 CS 验证 CA 信号

在中频下 IDD2N 电流降低 19%

在低频下降低 45%

这是对待机功耗的精准优化。

5. System Meta Mode(系统元数据模式)

LPDDR 系统需要元数据用于:

硬件配置

纠错信息

关键控制信号

过去版本使用独立引脚承载元数据。

LPDDR6 将元数据嵌入数据包内部(interleaved metadata):

减少专用引脚

降低电路复杂度

缩小面积

降低功耗

提升整体性能

这是接口层级的结构性优化。

标准与产业意义

JEDEC 于 2025 年 7 月 9 日发布 LPDDR6 标准(JESD209-6)。

LPDDR6 的目标场景包括:

AI 数据中心

高性能移动计算

智能手机

边缘设备

汽车智能系统

SK 海力士在 ISSCC 2026 上验证了:

1c nm 工艺

16Gb 容量

14.4Gb/s/pin

1.025V VDD2C

0.875V VDD2D

这意味着 LPDDR6 已经从标准走向实际硅验证阶段。

总体判断

LPDDR6 的升级并非简单“频率堆高”,而是:

架构级并行设计

时钟系统重构

终端匹配动态化

接口层元数据重构

它的定位已经从“移动 DRAM”升级为“高性能低功耗计算平台 DRAM”。

当 AI 工作负载开始向边缘与终端扩散,LPDDR6 的真正意义在于:

它试图用移动存储的功耗模型,承接数据中心级别的带宽需求。

这可能会重新定义高性能内存的分层结构。