本文要点

集成电路与 PCB 中均存在可能由开关数字信号激发的寄生效应。

所有高速数字集成电路都会产生一定的同步开关噪声,噪声的强度由集成电路结构和 PCB 布局中的寄生参数决定。

若要区分同步开关噪声与其他信号完整性问题,需要使用封装电感、I/O 线路和负载电容进行一些简单的计算。

观察眼图中的比特流或示波器上开关数字信号的波形,您可能会发现多种信号完整性问题同时显现,这是因为这些问题并非孤立存在。外部电路噪声、功率波动引起的抖动、背景热噪声、过冲、反射以及同步开关噪声都可能叠加在信号上。同步开关噪声(亦称“地弹”)尤为值得关注,因为它常被误判为其他信号完整性问题,即串扰和反射引起的过冲。

若要探究此类噪声的真正成因,我们需要分析集成电路中多个缓冲器同步开关时的工作机理(因此称为“同步开关噪声”)。集成电路和 PCB 的结构会产生寄生效应,从而在集成电路切换状态的瞬间激发强烈噪声。从电路角度剖析 PCB 与集成电路,有助于我们了解切换过程中的潜在问题以及使用电容的原因。

同步开关噪声的产生机理

若要探究同步开关噪声的成因,我们需要分析CMOS 缓冲器的结构、同一封装内各缓冲器之间的连接方式以及多个集成电路之间的连接方式。所有 CMOS 缓冲器均连接至同一个接地网络,并在系统主时钟的驱动下切换状态。当多个缓冲器连接至同一接地网络并同步开关时,会产生强烈的振荡,并叠加至目标信号电平上。

由于所有缓冲器同步开关,其产生的噪声会叠加至电路内的其他缓冲器上。在测量 I/O 线路相对于接地网络的输出信号时,由此产生的振荡在时域中清晰可见。通常情况下,我们可以使用示波器和高衰减比的电感式近场探头进行测量。 同步开关噪声特性

关于同步开关噪声,需掌握以下要点:

所有同步开关噪声均与 I/O 传输线中的电容和电感、接收器的输入电容以及互连两端的封装电感密切相关。

当更多缓冲器同步开关时,产生的振荡幅度更大(电压峰-峰值更高)。

虽然无法完全消除此类噪声,但只要选用合适的旁路电容,即可将振荡幅度抑制在足够小的范围,避免干扰接收端器件。

最理想的情况是,使振荡达到临界阻尼或过阻尼,但这需要在 I/O 引脚上添加一个较大的串联电阻。

要了解此类噪声的成因,以及同步开关噪声产生的物理机制,我们可以分析单个缓冲电路。

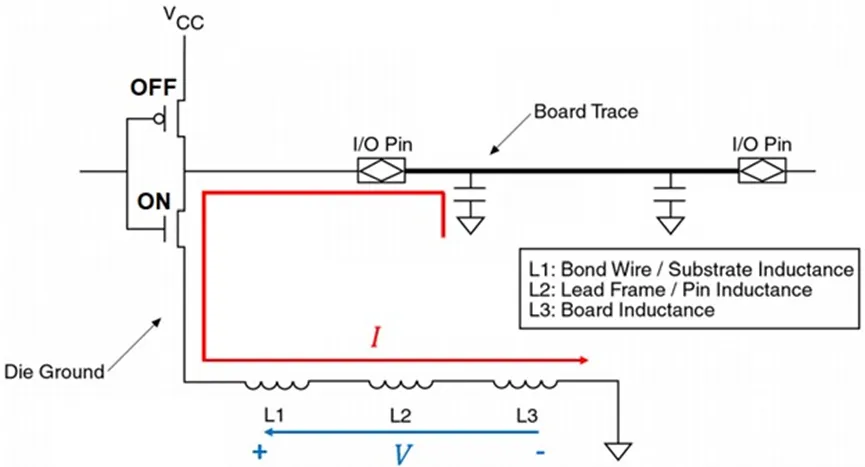

单个缓冲电路中的同步开关噪声

单个缓冲电路中的开关噪声与 I/O 传输线的电感和电容、接收器的负载电容、引脚封装电感以及信号路径中导体的直流电阻密切相关。下图展示了从关断状态切换到导通状态过程中的电流返回路径。正如我们所见,电压回路与电流路径均流经一个串联 LC 电路。

从关断状态切换到导通状态过程中的电流返回路径

由于上述串联 LC 电路的电阻趋近于零,其瞬态响应预期表现为欠阻尼振荡。这是所有阻尼极小的串联 LC 电路的典型行为。当高速数字集成电路中的多个缓冲器同步开关时,这些寄生效应便会引发前文所说的振铃现象。我们通常在集成电路的电源引脚与接地引脚之间添加一个旁路电容,通过旁路电容的放电来补偿接地参考电平的上移。 经验丰富的设计人员可能认为“这看起来很像串扰”,这种判断并无不当。不过,也可能是连接两个器件的短走线发生了共振。

地弹、串扰与谐振

从示波器波形来看,这三种信号完整性效应的表现可能非常相似,而且还可能同时发生,从而形成时域中所见的复杂行为。若要区分这些效应,需要利用互连线中的电容和电感参数进行一些基础计算。

专业的 PCB 设计工具通常集成 3D 场求解器,可用于从 PCB 布局中提取串扰耦合参数。基于这些参数,不仅能确定任何电压峰值的预期大小与瞬态振荡频率,还可直接获得串扰引起的时域响应。这有助您判断互连线中的噪声究竟是同步开关噪声、串扰、谐振,还是这些效应的叠加。 文章来源:cadence