作者: THOMAS KUHR,WOLFSPEED 公司工艺制程开发工程高级总监

我们能将碳化硅 (SiC) 衬底厚度推进到多薄而不影响性能?这是我们几十年来一直在追问的问题,同时我们也在不断突破碳化硅 (SiC) 材料性能的极限——因为我们知道下一代碳化硅 (SiC) 器件技术正依赖于此。

这篇文章探讨了 Wolfspeed 在碳化硅 (SiC) 衬底的成本、可扩展性和质量等最严峻挑战方面的研究,包括了碳化硅 (SiC) 外延和衬底厚度如何影响高电压器件。

碳化硅 (SiC) 衬底的成本需要降下来。但是,如果我们对这种基础材料的厚度施加限制的话,会阻碍这些努力吗?

碳化硅 (SiC) 正受益于电动汽车的蓬勃发展。基于这种宽禁带半导体的功率器件的采用,使得更高效率的电子设备能够将系统损耗降低 80% 甚至更多。然而,尽管这令人印象深刻,但这只是其好处的冰山一角。和其他宽禁带材料一样,碳化硅 (SiC) 还具有高热导率和优异的饱和漂移速度,使得用这种材料制成的器件能够在高电场密度下工作,并应用于许多技术领域,包括高电压直流、脉冲功率和固态变压器。使用可处理高达 10 kV 的单个碳化硅 (SiC) MOSFET 芯片,甚至更高电压的双极器件,为设计人员提供了简化系统并在许多应用中降低电阻加热损耗的机会。

随着碳化硅 (SiC) 持续展现出优于现有技术的改进性能,其较高的成本正受到重点关注。在半导体行业内,应对这一挑战的常见解决方案是转向更大尺寸的晶圆,从而将固定的加工成本分摊到更多的器件上。这一转变正在进行中,碳化硅 (SiC) 衬底目前正经历从 150 mm 直径向 200 mm 直径的转型。然而,与随着直径增加而增加晶圆厚度的硅 (Si) 行业不同,碳化硅 (SiC) 行业正在考虑为 200 mm 直径晶圆保留现今 150 mm 直径晶圆所使用的 350 µm 厚度。

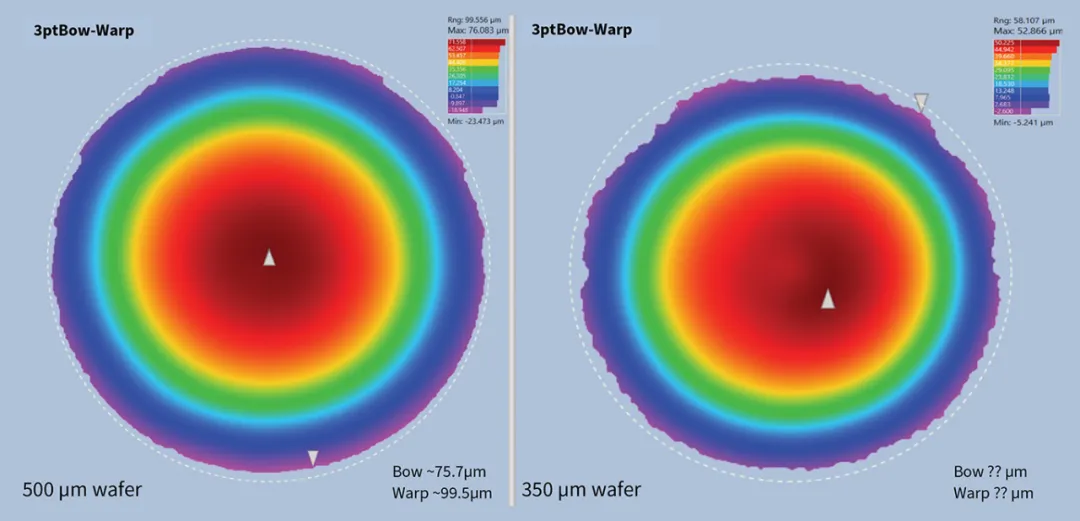

图 1. 500 µm 厚度(左)和 350 µm 厚度(右)的晶圆形状图比较。请注意,在这两种情况下都未生成完整的图谱,不过左侧的扫描更完整。350 µm 厚度晶圆的弯曲度(Bow)和翘曲度(Warp)明显更高,超出了当前工具配置的测量范围。

Wolfspeed 作为全球碳化硅 (SiC) 衬底和器件的领先企业,我们一直在研究,当采用 350 µm 厚度和 500 µm 厚度的晶圆时,不同厚度条件下的外延层在质量上有何差异。用于制造 650 V 和 1200 V 器件的“薄” 碳化硅 (SiC) 层的生长,往往不会因温度情况或衬底与外延膜层之间掺杂差异而产生显著应力。然而,当外延层更厚且掺杂浓度更低时——这是更高击穿电压器件的两个关键要求——应力会被放大,产生新的缺陷并引发晶圆形状问题。

此外,外延缺陷的尺寸和面积也会增加,因为它们通常在衬底界面处或附近产生,并随着薄膜的生长而相应增大。更大的应力和更大的缺陷,加上高电压器件通常尺寸更大,这些因素的复合效应导致晶圆的可使用面积大大降低,从而导致芯片良率降低和每个器件的成本升高。

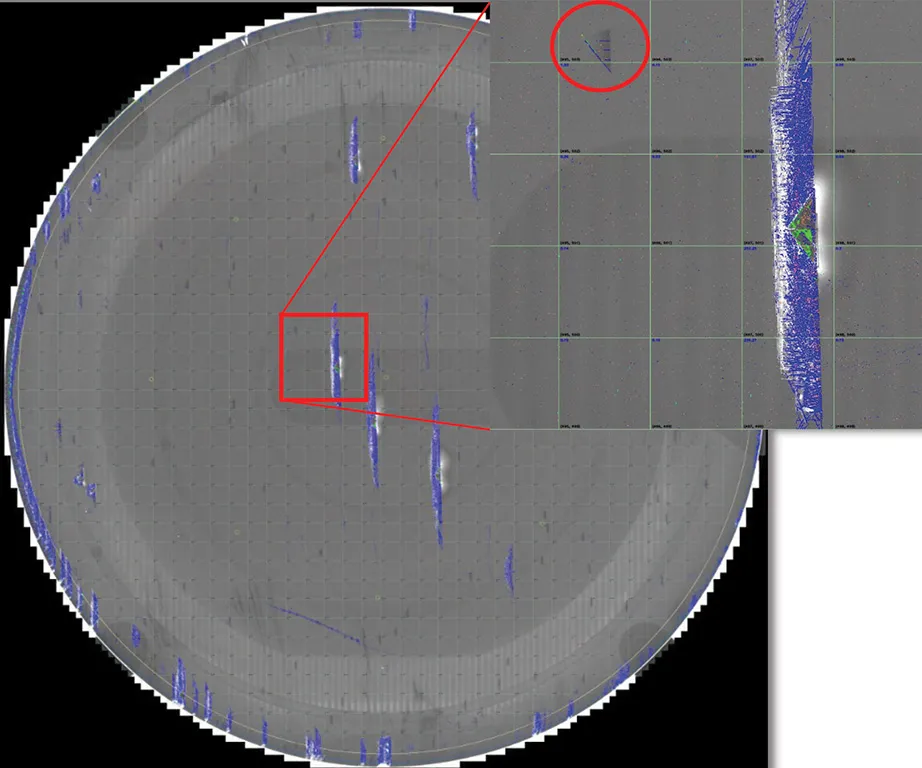

图 2. 用于估算 500 µm 厚度 200 mm 直径衬底上生长 115 µm 厚度外延层的器件可用面积的拼接图像图(带有初步墨迹标记)。使用了任意的 5 mm x 5 mm 网格进行可视化。请注意,并非所有缺陷都被正确识别,但可以看到宏观缺陷(如三角形缺陷)的面积效应,如插入图片所示。

可能会出现什么问题?

为了加深我们对更薄衬底和更厚外延层之间相互作用的理解,我们研究了三种不同厚度的同质外延层的性能对比。外延层在 350 µm 厚度和 500 µm 厚度的 200 mm SiC 衬底上进行生长,并采用了两种已商用的反应器平台。诚然,进行这种评估的最佳方法是将单个晶锭切割成多个不同厚度的衬底,因为这样可以标准化衬底缺陷的起始点。但在这项工作中,我们使用了内部生产的晶圆因为它们已经可获取的。我们根据特定的器件要求选择了掺杂和厚度目标,旨在达到所需击穿电压下的最低电阻,并且通过利用我们标准生产流程中的一套测量方法,我们已经能够确定是否存在任何潜在的制造限制。

外延生长过程中的一个担忧是晶圆形状在高温生长条件下的稳定性。晶圆形状在室温和超过 1600 °C 时可能不同,更薄的晶圆可能会不可预测地改变形状。任何变化都会通过厚度或掺杂不均匀性对生长产生不利影响。在最坏的情况下,晶圆可能会在加工过程中破裂或从承载器上弹出。

我们的结果消除了将晶圆厚度从 500 µm 减少到 350 µm 时的这种担忧。如果说有什么不同的话,更薄的晶圆反而改善了薄膜厚度和掺杂均匀性,尽管这可能取决于反应器设备的设计。请注意,我们需要进行更多轮的生长实验才能建立具有统计显著性的结论。然而,我们的初步研究表明,在外延生长过程中使用更薄的 200 mm 晶圆不存在相关问题。

由于薄型和厚型碳化硅 (SiC) 器件在加工化学和器件设计方面的相似性,我们的器件制造团队希望所有外延晶圆的表面状态相似。为了验证是否如此,我们使用原子力显微镜(AFM)和共聚焦成像技术仔细检查了我们的材料。用于测量短程粗糙度的 AFM 显示,粗糙度性能相匹配,薄膜和厚膜的平均粗糙度(Ra)均小于 0.2 nm。根据共聚焦成像,厚膜的长程粗糙度大于薄膜,平均粗糙度(Ra)约为 0.6 nm。

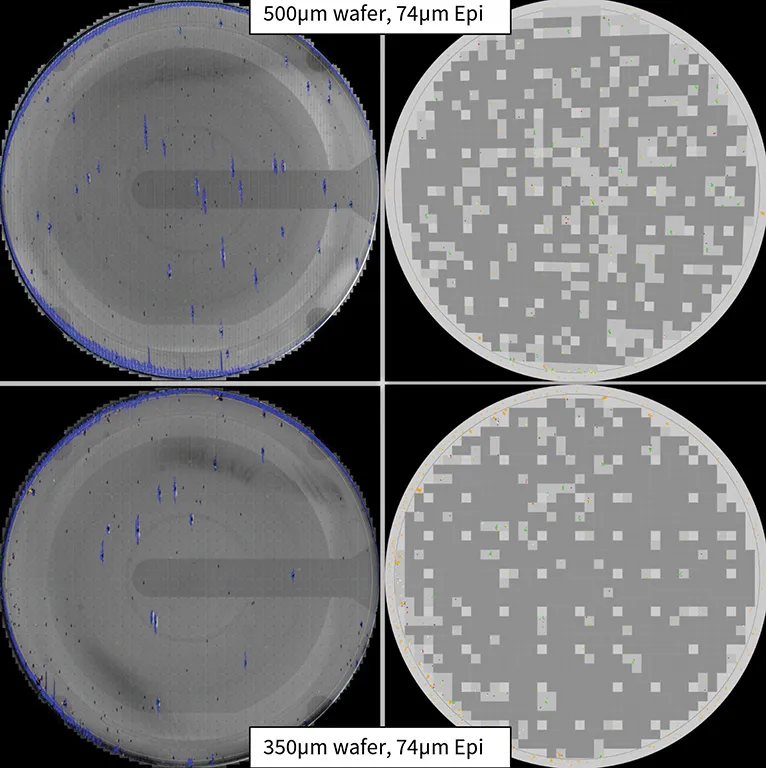

图 3. 用于估算 500 µm 厚度和 350 µm 厚度 200 mm 衬底上生长 74 µm 厚度外延层的器件可用面积的拼接图像图(带有初步墨迹标记)。显示了 75-85% 的 5x5 可用区域。

这些发现与衬底厚度无关,尽管在共聚焦成像尺度上,稍微多一点的粗糙度在空间分布上略广一些。这表明,就像掺杂和厚度均匀性一样,表面粗糙度相对于晶圆厚度而言可能不是一个问题。然而,有必要减少厚膜的表面粗糙度,并进一步改进空间依赖性。

由于更厚的外延层会导致更大的缺陷和更高的薄膜应力,选择更薄的衬底会加剧应力问题。因此,当在更薄的衬底上生长更厚的外延层时发现形状问题,我们并不感到惊讶。使用直径 200 mm 的碳化硅 (SiC),在 500 µm 厚度的衬底上生长 13 µm 厚度的外延层会导致 20-40 µm 的弯曲度 (Bow);将厚度增加到 115 µm,并将掺杂浓度降至 10^15 cm^-3 的中段,弯曲度会增加至 80 µm 左右。如果然后将衬底减薄至 350 µm,弯曲度会增加至 100 µm 以上,从而在器件制造过程中带来处理错误和晶圆破裂的风险。虽然 100 µm 的晶圆弯曲度与离子注入过程中可能发生的数百 µm 弯曲度相比似乎微不足道,但并非所有的制造工具都能从那个起点开始处理。我们的观点是,如果打算采用仅 350 µm 厚度的衬底来生长更厚的外延层,可能需要做更多的工作来补偿晶圆形状问题。

碳化硅 (SiC) 最大的缺点是其晶体生长过程中固有的缺陷性以及相对容易形成缺陷。在晶锭生长过程中产生并存在于衬底中的缺陷,要么通过生长的延续,要么通过转化为其他类型的缺陷,传播到外延层中。缺陷的来源可能是微管、穿透位错 (threading dislocations)、堆垛层错 (stacking faults)、表面制备造成的亚表面损伤,或者仅仅是清洁不充分导致的脏污表面;更一般地说,任何破坏晶格自然堆叠的因素都会导致缺陷。例如,一种称为“三角形”的常见缺陷——它是一种晶体堆叠紊乱,表现为生长表面可见的三角形——其尺寸随着外延生长而增大,从外延生长 13 µm 时的 0.4 mm 长增加到 115 µm 厚薄膜时的 3.2 mm。您可能会想,这有什么大不了的,因为器件通常尺寸为 25 mm^2 或更大,所以一个三角形缺陷应该只影响一两个芯片。

正如我们已经提到的,薄膜应力随着厚度以及薄膜与衬底之间的掺杂差异而增加。因此,加上碳化硅 (SiC) 基平面位错 (basal plan dislocations) 非常低的形成能 (formation energy),诸如三角形之类的缺陷有可能产生基平面位错。这些位错从源缺陷处出现,沿着晶圆垂直滑移。因此,一个最初只影响一两个器件的缺陷现在可能会影响五到十倍的芯片,从而大幅降低良率。

好消息是,通过精细管理外延生长过程中晶圆上的温度分布,可以减少过度的薄膜应力。即使这种收益是以增加晶圆弯曲度为代价,这也使得能够处理更薄的晶圆而不会增加薄膜缺陷。

不巧地是,并非我们所有的测量都特别顺利。由于扫描不完整,我们最初关于带有厚外延层的薄晶圆的最大弯曲度数值是不正确的。我们花了一点时间和精力,通过微小调整,克服了这个简单工具限制,纠正了这个错误。

图 4. 准备进行封装的 10 kV 裸芯片。

我们还遇到了与缺陷自动检测相关的问题,原因是检测算法是针对不同尺寸的缺陷或更光滑的表面进行训练的。这意味着我们将应用于更薄外延层的准确的缺陷分类和数据采集方法,用在更厚外延薄膜的初期阶段会遇到困难。

我们遇到的与晶圆弯曲度扫描和缺陷检测相关的问题并非不可克服。就缺陷而言,它们甚至与衬底厚度无关。然而,在这些技术能够服务于大批量制造工艺之前,需要进行干预和开发。

总而言之,更薄的晶圆会导致形状问题,必须在外延生长之前或生长期间解决。但如果温度分布和应力得到有效管理,额外的应力诱导缺陷应该不会成为问题。这听起来还不错,除了预测的良率看起来并不那么高,而且成本仍然很高。

为了说明这一点,我们考虑用于 1200 V MOSFET 晶圆的 5 mm x 5 mm 器件。在这种情况下,可用面积超过 90%。但如果需要更厚的外延层,由于增大的面积效应,可用面积会下降到 70% 左右。如果器件尺寸增加,根据简单的泊松统计,可用面积会进一步下降。现在,那片对于 1200 V MOSFET 可用面积超过 90% 的碳化硅 (SiC) 晶圆,对于 10 kV MOSFET 而言可能低于 40%,而这甚至是在外延片进入器件制造厂之前。

图 5. 高性能半桥 10 kV、 50 mΩ 全碳化硅 (SiC) 功率模块。

可行的厚度?

让我们回到最初的问题:减薄碳化硅 (SiC) 衬底是否会限制使用更厚外延层制造高电压器件的能力?嗯,也许吧……也许不会。很明显,关键是要控制晶圆形状并管理外延生长应力,以防止器件制造过程中的复杂情况,从而保持低成本。为了支持这些努力,需要进行调整以确保测量和计量方法与当前最佳实践和行业标准保持连续性。但同样非常重要的是,碳化硅 (SiC) 衬底制造商需要继续专注于减少缺陷。如果没有更低的缺陷浓度,器件尺寸和能力或器件良率将继续需要权衡取舍,并且无论外延生长过程如何优化,成本都将保持高位。

最后,推动碳化硅 (SiC) 衬底变得更薄的努力将继续下去,因为降低其成本仍然是一个巨大的动力。在此背景下,创新者将找到处理晶圆形状的方法,衬底制造商将继续降低缺陷密度,有助于提高器件良率并削减成本。

出于纯粹的技术需求,对于更高电压器件的使用将继续提升,采用 10 kV MOSFET 或更高电压的 IGBT 将为其铺平道路。碳化硅 (SiC) 变革正逢其时!

此文章的中文翻译仅供参考,相关信息请以英文原稿为准。

文章来源:Wolfspeed