半导体器件是由数百层材料薄膜经多次沉积与刻蚀堆叠而成。为确保整个芯片区域及硅晶圆表面形成均匀结构,工艺工程师需要设计最优的沉积与刻蚀工艺组合。均匀度则是半导体制程中最常见且核心的控制参数,其中刻蚀均匀度尤为关键。

刻蚀速率受到多种物理机制的影响, 这使得刻蚀均匀度控制面临严峻挑战。此外,特定的刻蚀机制会根据刻蚀工艺环境中的具体物理条件,产生相反的刻蚀倾向(或刻蚀图形)。工艺工程师需要准确评估这些机制的影响,以实现对刻蚀工艺的精准调控。在本研究中,我们通过建立工艺模型,提出了一种研究虚设图形工艺、提升刻蚀均匀度的简易方法。采用该方法,工艺工程师能够基于可预测的刻蚀机制与行为,获得符合预期目标的均匀刻蚀结果。

刻蚀负载效应机制

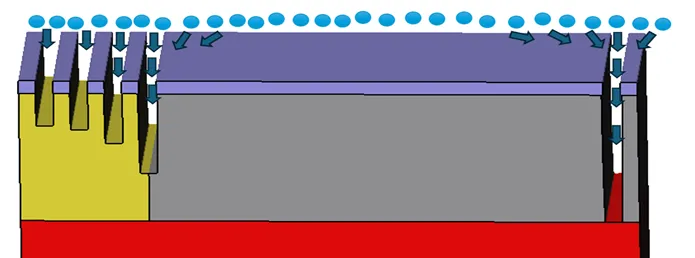

我们首先通过两种不同的刻蚀行为来深入理解常见的刻蚀负载机制。第一,在密集、大面积的图形区域,由于化学反应气体消耗速度更快,其刻蚀速度会小于稀疏、小面积的图形区域。当刻蚀区域的图形密度高至表面及近表面的刻蚀剂被完全消耗时,后续刻蚀将缺乏反应物以深入材料内部,从而导致其刻蚀速率减缓、深度变浅。相比之下,稀疏图形区因仍有足量刻蚀剂,得以维持正常的刻蚀深度。因此,图形密集的大暴露区域会因刻蚀剂浓度不足而呈现较低的刻蚀速率(图1)。

图1:密集区域的化学物质消耗会导致相对较慢的刻蚀速率

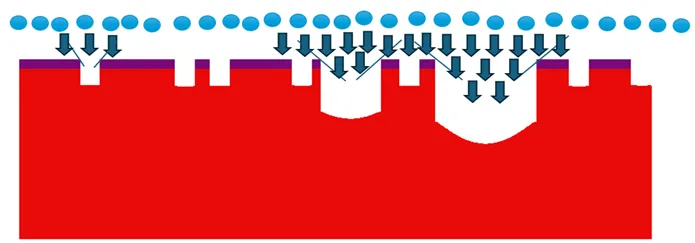

第二,反应物进入结构的开口尺寸会影响刻蚀速率。更大的开口能使更多刻蚀剂到达被刻蚀结构的表面。若开口尺寸大,刻蚀剂或化学反应粒子便可深入图形内部,实现更深的纵向刻蚀(图2)。

图2:宽开口可以导入更多刻蚀剂。只要刻蚀剂总量足以完成全过程,宽开口结构就能使刻蚀进程快于窄开口结构

负载效应下的刻蚀工艺模拟

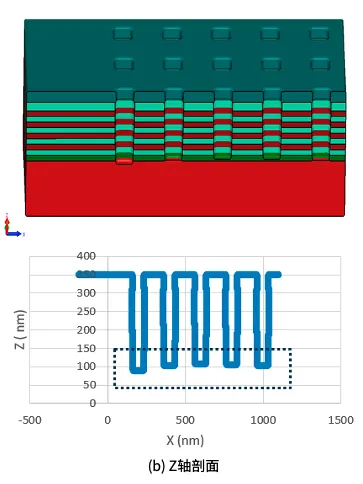

我们首先创建了一个基础刻蚀仿真模型(图3),包含均匀分布且开口尺寸一致的孔洞图形。我们在结构上进行刻蚀模拟,结果表明,由于图形边缘孔洞对刻蚀剂的消耗,结构中心区域的孔底刻蚀深度不足。虽然可以通过增加刻蚀总量(或刻蚀时间)进行补偿,却会引发结构左右边缘孔洞的过度刻蚀问题(图3)。

图3: (a) 基础刻蚀模型模拟的结果表明,因边缘孔洞刻蚀剂消耗更快,导致中心刻蚀深度较浅;(b) Z轴剖面,孔底最大高度差约27nm

图形设计优化

针对刻蚀负载效应,本研究评估了两种提升深度均匀度的方法。其一是在模型左侧孔洞附近添加虚设图形线条,通过邻近虚设图形所产生的额外化学反应物消耗,将相应减缓左侧边缘孔洞的刻蚀进程(图4)。模拟结果表明,此方案可将孔底最大高差从27nm优化至10nm,均匀度获得显著提升。

图4: (a) 在左侧边缘孔洞旁设置虚设图形后的刻蚀模型结果;(b) Z轴剖面,显示孔底最大高度差约为10nm

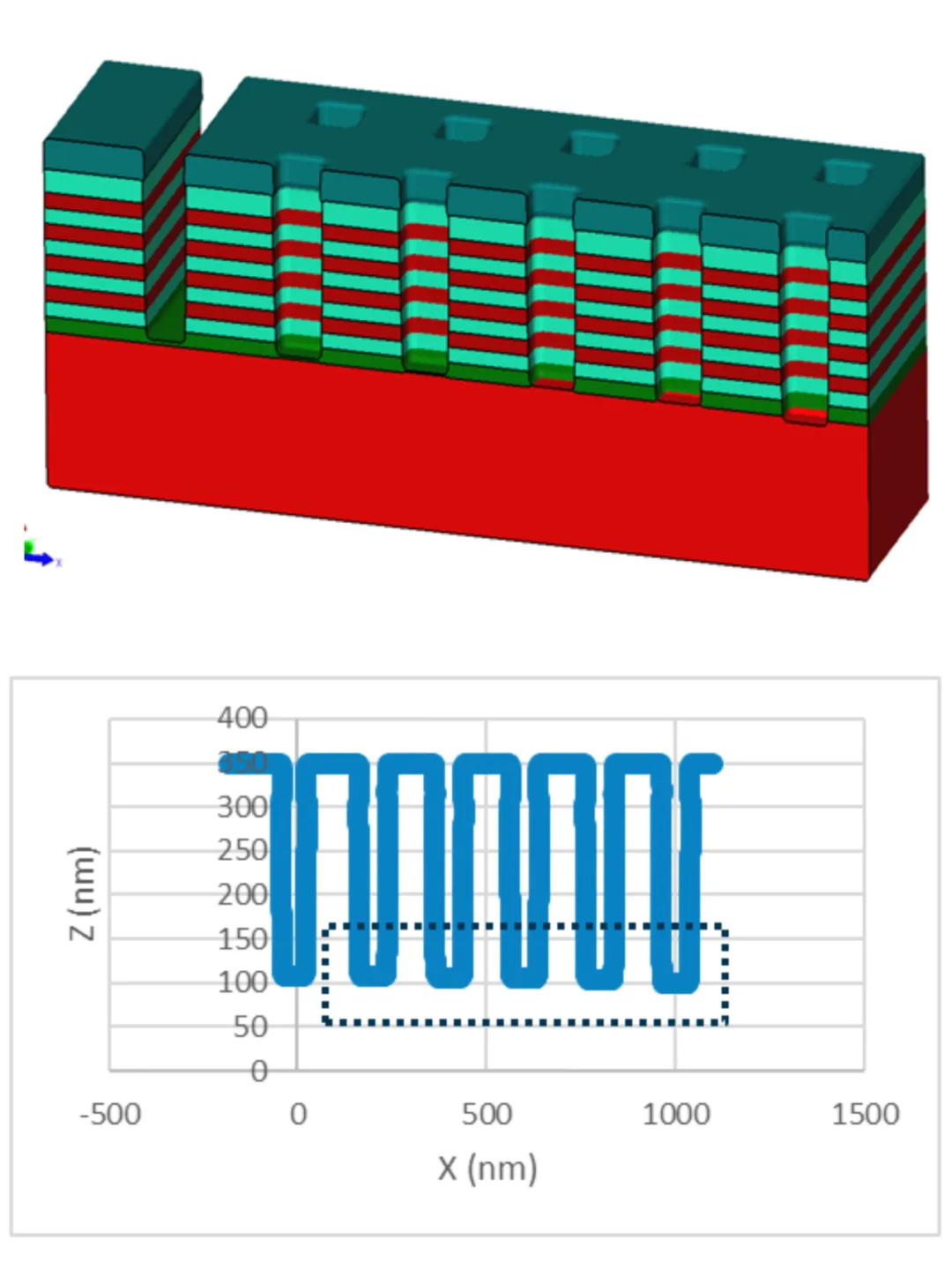

第二种方法是通过调整结构左上方的硬掩膜开口尺寸来控制左侧边缘孔洞的刻蚀速率。扩大开口能够使更多刻蚀剂进入,从而加快该区域的刻蚀速度,这一现象基于微负载效应。通过我们的仿真发现,采用这一方法后,孔底最大高度差由27nm降至8nm。与添加虚设图形线条的方法相比,该技术的刻蚀均匀性略有提升。

图5:(a) 在结构左侧设置更大开口后的刻蚀结果; (b) Z轴剖面,孔底最大高差约8nm

利用仿真技术补偿刻蚀工艺失效

工艺工程师始终致力于将刻蚀负载效应最小化,保持卓越的工艺均匀度。然而,仅通过调整设备的刻蚀参数来补偿负载效应往往难以实现——工程师可能受限于设备本身的工艺能力,或是受制于狭窄的工艺窗口而无法对设置进行大幅调整。在此情况下,通过修改布局设计来应对负载效应,是一种有效的替代方案。通过添加虚设图形或调整刻蚀区域的尺寸,能够有效改善由负载效应引起的刻蚀均匀度偏差。

然而,若依赖硅晶圆测试来评估这些布局改动对刻蚀均匀度的实际影响,成本高昂且耗时。相比之下,利用工艺建模与虚拟制造技术,能够实现对设计方案高效且快速的验证。这类高精度模型扮演着“虚拟刻蚀孪生”的角色,能够精准预测实际刻蚀行为。借助虚拟孪生,工程师能够快速确定最优的虚设图形设计方案,无需在硅晶圆实验上花费过多的时间和成本。

结论

本研究中,我们提出了一种基于工艺建模的简易方法,来研究虚设图形技术并提升刻蚀均匀度。通过该方法,我们能够解答“如何布局虚设图形以补偿刻蚀负载效应并提高均匀度”这一关键问题。而答案,正存在于运用虚拟刻蚀孪生所构建的工艺模型之中。