问:为什么 PLL(锁相环) 能确保速度多级采样的抗干扰性与准确性?

PLL(锁相环)的框图通常包含鉴相器(Phase Detector, PD)、环路滤波器(Loop Filter, LF)、压控振荡器(Voltage-Controlled Oscillator, VCO) 三大核心模块,部分场景会加入分频器或信号预处理单元。

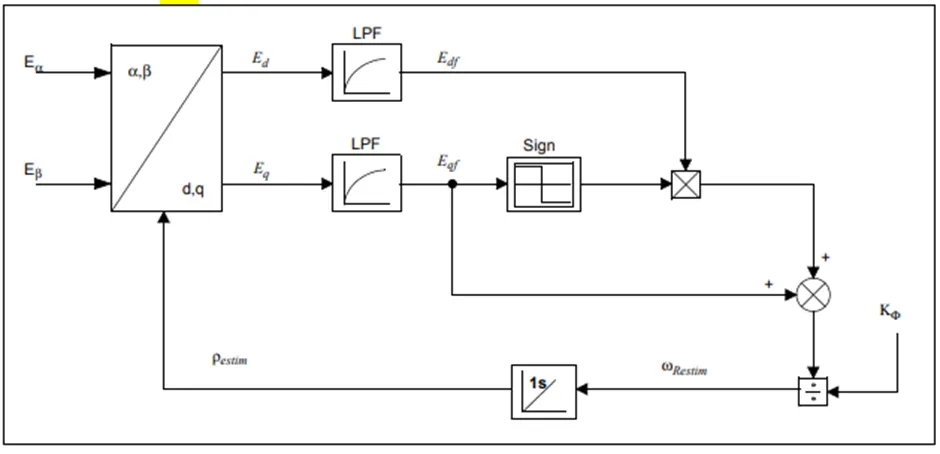

PLL(锁相环)框图 (图片来源于Microchip)

- 鉴相器(PD):对比输入的速度关联信号(如电机电流交变信号、编码器脉冲信号)与 VCO 输出信号的相位差,将相位差转化为误差电压;

- 环路滤波器(LF):对误差电压进行滤波(如低通滤波),抑制高频噪声和瞬时干扰,输出平滑的控制电压;

- 压控振荡器(VCO):根据控制电压调整输出信号的频率 / 相位,使其逐步逼近输入信号的特性,最终实现“锁相”—— 输入与输出信号频率一致、相位差稳定。

- 抑制频率混叠:根据奈奎斯特采样定理,采样频率需至少为信号最高频率的 2 倍。PLL 通过 VCO 动态调整采样时钟频率,使其始终跟踪输入信号的频率,避免因采样率固定导致的低频段过采样冗余或高频段欠采样混叠。

- 抵抗动态干扰:当速度突变(如多级切换瞬间)时,输入信号频率会剧烈变化。PLL 的环路滤波器可平滑误差信号,VCO 快速响应调整输出频率,确保在过渡过程中仍能稳定跟踪信号。

- 降低相位噪声影响:环境电磁干扰会导致信号相位抖动,PLL 的闭环反馈可通过相位修正抵消抖动,使输出信号相位稳定。