除了晶体管架构的升级,英特尔还通过PowerVia背面供电技术,将电源线从晶体管正面迁移到背面,显著改善了晶体管布线,从而进一步提升了芯片的性能和能效比。

在本期“5分钟IN科普”中,让我们跟随电源线一起“搬家”!

芯片中的“城市”与“居民”:电源线与信号线

我们日常使用的手机和电脑,里面的芯片通常由几百亿个晶体管组成。如果我们把它比作一座超大型的城市,那么晶体管就是里面的居民。 市民需要电、水和燃气才能生存,电源线就好比城市里的输电线、自来水管和燃气管道,保障晶体管的基本运作。晶体管本身并不产生能量,而是通过电源线将外部能量引入电路,源极与漏极之间在电源电压的作用下形成电势差,沟道被建立,电流才得以通过晶体管流动。 信号线则好比光纤和电话线,让居民们能够互相交流,也就是负责在晶体管之间传递指令和数据。通过调节栅极电压,晶体管可以在“开”和“关”之间切换。一个晶体管的开关状态,会改变电路中某个节点的电压水平,这个电压通过信号线传递到下一个晶体管的栅极,控制它的工作状态。正是这种电压的高低变化,使得“0”和“1”的二进制信息能够在芯片内部不断传递。 从专业视角看,这个“城市比喻”虽形象,但实际芯片设计还需考虑电源分配网络(PDN)、信号完整性(SI)、互连延迟等复杂因素,需要协同设计以确保系统在高速下的稳定运行。

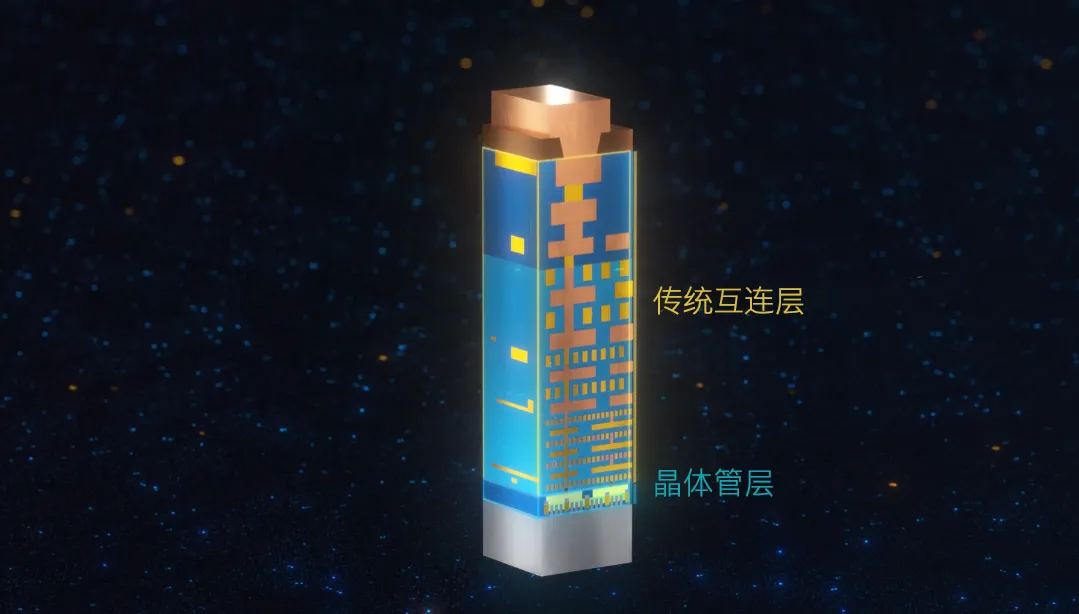

“披萨”式堆叠的挑战:传统正面供电

长期以来,芯片制造普遍采用正面供电技术,信号线和电源线都位于晶体管上方。这好比制作披萨,从硅衬底开始构建晶体管,再在其上逐层堆叠金属层用于布线和供电。 在早期制程节点中,晶体管尺寸较大,布线空间相对充裕。然而,随着制程持续微缩至纳米级别,挑战日益凸显: ● 布线拥塞:晶体管上方空间日益狭窄,电源线与信号线相互竞争有限资源。 ● 性能瓶颈:电源线变细导致电阻增加,电流经由上方多层金属层到达晶体管时,电压降(IR Drop)加剧,引发功耗、发热问题,并影响晶体管速度与信号质量。

正面供电

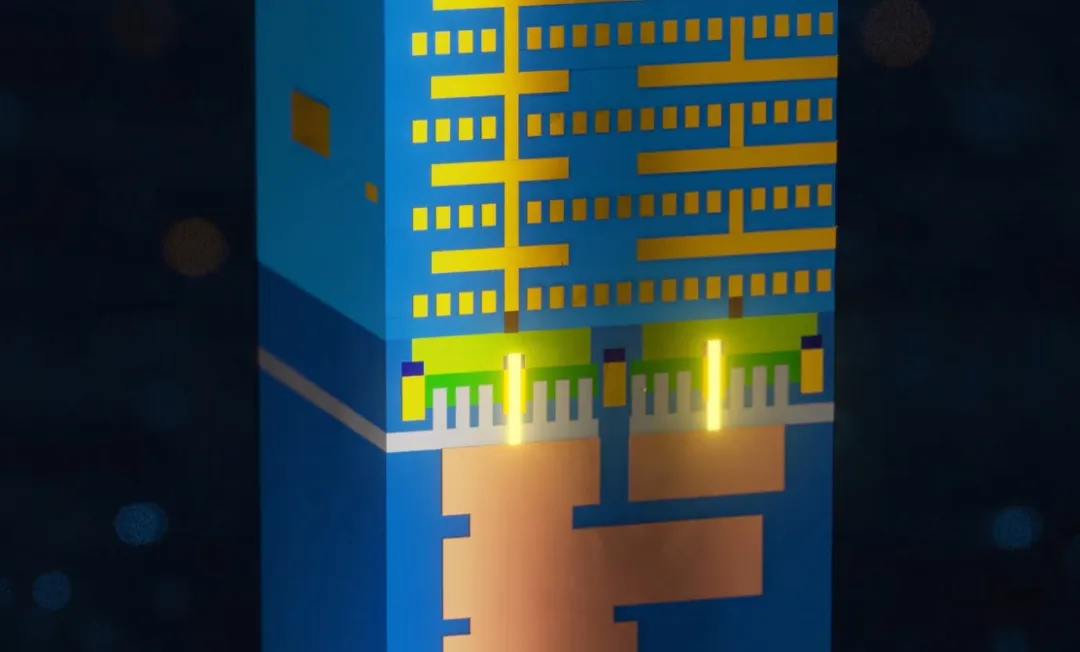

精巧的“三明治”工艺:背面供电的实现

为应对上述挑战,英特尔率先推出PowerVia背面供电技术。它将电源线“搬迁”至晶体管背面,使晶体管层如同三明治的夹心,位于电源线与(正面的)信号线之间。 实现这一结构的关键步骤包括:在硅衬底上制造晶体管后,将其翻转、背面减薄并抛光,然后刻蚀出硅通孔(TSV) 连接背面的电源线。之后,芯片被翻回正面,连接正面的信号线。在PowerVia技术中,电流从背面电源线经TSV到达晶体管上方的金属层,再供给晶体管。 更短、更省、更稳定:背面供电的优势

● 提升能效:供电路径大幅缩短,显著改善了电压降,既提升了性能,也降低了能耗。 ● 节约空间:有效利用晶体管背面空间,缓解了正面布线拥塞,有助于集成更多晶体管。 ● 改善信号完整性:电源线与信号线分离,减少了相互干扰,使信号传输更稳定。

硅通孔

未来的方向:更直接的连接 展望未来,业界正在探索如PowerDirect般的直接背面触点技术。与PowerVia相比,它旨在通过背面触点将电源线更直接地连接到晶体管的源极或漏极,进一步缩短供电路径,降低电阻,持续推动芯片性能与能效的边界。 从“披萨”到“三明治”,这场给电源线“搬家”的革命,是芯片制造工艺的一次精巧升级,是持续释放算力潜能的智慧体现。未来,随着技术的进步,期待我们手中的智能设备变得更强大、更高效。 文章来源:英特尔中国