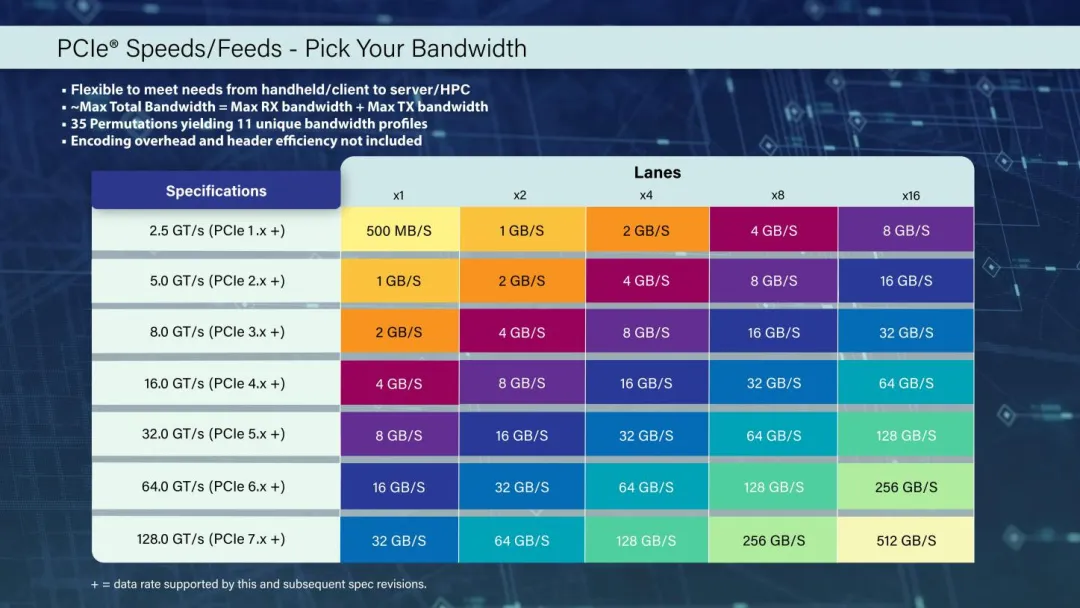

随着大规模计算集群与云数据中心不断扩展升级,PCI Express总线正加速迈入PCIe 7.0 时代。其带宽由PCIe 5.0的32GT/s跨越至128GT/s,×16单方向带宽可达512GB/s,仍然是CPU、GPU、加速器、DPU与存储系统之间的主力互联标准。在这一速度等级下,平台对时钟分配、抖动控制、同步一致性及信号完整性的要求远超以往。因此,PCIe 7.0时钟缓冲器(Clock Buffer)成为新一代系统架构中不可或缺的芯片。

图片来源:PCI-SIG官网

PCIe7.0时钟缓冲器的作用

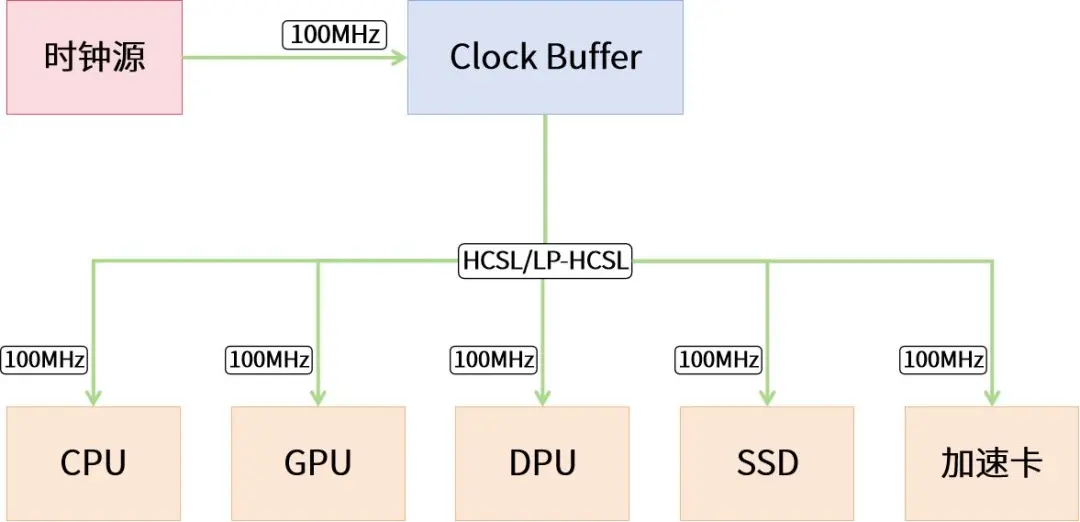

在PCIe架构中,时钟缓冲器(Clock Buffer)是关键组件,用于从参考时钟源(通常为100MHz)以极低附加抖动的方式分配至CPU、GPU、DPU、SSD、加速卡以及主板上的各类高速器件。它确保所有下游设备同步运行,支持源同步时钟(Source-Synchronous Clocking)模式。时钟缓冲器通常采用HCSL(High-Speed Current Steering Logic)或LP-HCSL(Low-Power HCSL)输出接口,以减少组件数量和PCB布线复杂性。随着PCIe7.0的来临,时钟缓冲器需应对更高的频率(Nyquist频率达32 GHz)和更严格的抖动预算,以维持信号完整性。

PCIe7.0时钟缓冲器的应用

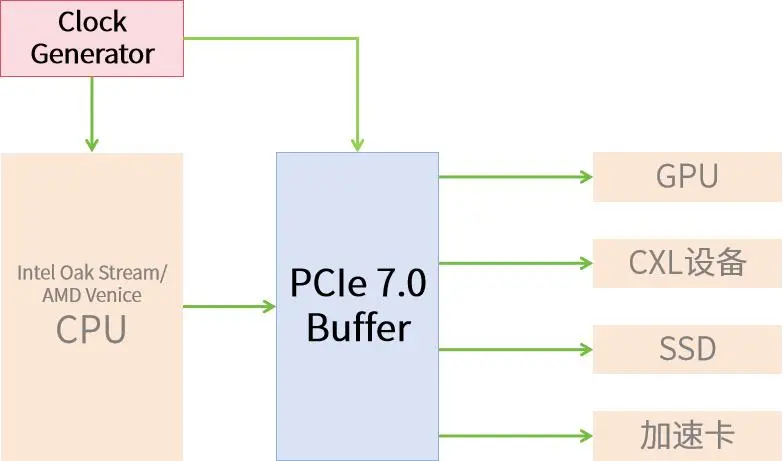

面向下一代服务器平台,Intel Oak Stream与AMD Venice均全面支持PCIe6.0,并将继续向PCIe7.0演进,使主板时钟网络在带宽、同步性与抖动性能方面面临更高要求。两大平台均采用外置高精度时钟缓冲器(Clock Buffer),将主时钟源的100 MHz参考时钟稳定扇出至GPU、CXL设备、SSD、加速卡及OCP模块化接口,确保系统在128GT/s PAM4链路下维持统一、低噪声的时钟环境。在这些新平台中,PCIe7.0时钟缓冲器已不再只是简单的时钟分配器件,而是支撑平台带宽释放、链路稳定与长期可靠运行的关键基础设施。

星拓微电子推出PCIe7.0时钟Buffer TBUF23xx系列时钟Buffer是星拓微电子专为新一代CPU平台设计。该系列(包括TBUF2324A、TBUF2320A、TUBF2312A、TUBF2308A、TUBF2324A、TBUF2324B等型号)提供4~24个LP-HCSL输出,附加相位抖动低,支持Common Clock(CC)和Independent Reference(IR)架构,兼容SMBus配置和Side-Band Interface(SBI)。完全满足PCIe7.0规范对参考时钟的极端低抖动要求,附加相位抖动低至3 fs RMS以下(PCIe Gen7),同时向下兼容PCIe Gen1~Gen6,并符合Intel DB2000Q标准,适用于多Socket系统时钟分发。完美适配Intel Oak Stream、AMD Venice等新一代CPU平台。 产品特性 满足PCle1.0~7.0时钟规范 支持LP-HCSL,满足DB2000QL标准 HCSL/LVDS输入 LP-HCSL差分输出,最高400MHZ 选型推荐 文章来源:星拓微电子