Qorvo首席系统工程师/高级管理培训师 Masashi Nogawa将通过《从射频信号完整性到电源完整性》这一系列文章,与您探讨射频(RF)电源的相关话题,以及电源轨可能对噪声敏感的RF和信号链应用构成的挑战。我们之前对电压调节器模块(VRM)输出阻抗ZOUT及相关主题进行了多方面探讨。这篇文章将从一个新的角度聚焦这个话题——VRM的输出阻抗如何影响时域中的噪声;在未来的文章中,我们还将更深入地探讨其学术方面的话题。

关于噪声可以找到很多优秀的书籍、论文及在线文章;因此,本文不再赘述噪声的基本原理,而是会从信号完整性(Signal Integrity,SI)和电源完整性(Power Integrity,PI)的角度出发,讨论如何切实管理噪声。

VRM系统中的噪声

通常,就噪声而言,噪声越低,系统状况就越好——当然,前提是无需为此付出任何代价。

在本文中,我们将研究获得低噪声VRM所需付出的这些代价。

关于处理噪声,我们都知道以下简单的规则:

降低输出节点的(VRM输出)阻抗可降低该节点的噪声 增加节点的偏置电流可降低噪声 让电路/PCB在较低的温度下运行可降低噪声

对于规则1阐述的降噪技巧,在目标节点接入旁路电容是一种简便而有效的手段。

规则3直接涉及热噪声的降噪方法。

最后,规则2是第1条和第3条规则间的权衡。通过增加电路的偏置电流,我们依照欧姆定律(V=R×I)降低了目标节点的阻抗。

当工作偏置“电压”点保持不变时,增加电流“I”意味着降低阻抗“R”。然而有趣的是,增加偏置电流会提升系统的功耗或功率损耗,从而导致电路板温度升高和热噪声增大。

回到第1条规则,我们最简单的操作就是添加电容,但我们在本系列文章中已经回顾过,VRM具有低输出阻抗。

增加VRM环路电容

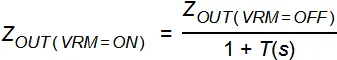

通常在VRM系统中,ZOUT(VRM = OFF)项对应输出电容。根据等式9-1,在调节器带宽内,VRM环路增益可以降低输出电容的阻抗;且这是一种显著的阻抗降低。

《ZOUT到NISM:输出阻抗到非侵入式稳定性测量》中的等式9-1

VRM在其输出节点处起到主动降噪模块的作用,这也是为什么我们在噪声敏感的射频(RF)和信号链设备附近会发现许多LDO(低压差线性稳压器)。

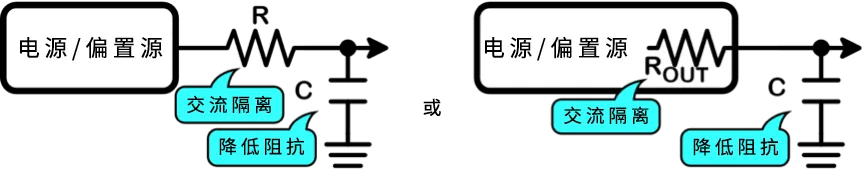

相比于简单地放置电容,ZOUT(VRM=ON)带来的这一优势非常重要。额外的电容有助于降低噪声的基本机制是形成RC滤波器;这种滤波器通过一定值的电阻R隔离上游电源/偏置源电路;这里电阻R可以是一个明确的电阻元件或固有源的输出阻抗。然后,目标节点的阻抗被电容C降低到一个非常小的数值,从而进一步减少了噪声。

图12-1,作为噪声旁路的RC滤波器

在处理PI或电源分配网络(PDN)阻抗时,我们关注的阻抗远低于1欧姆(Ω),并且我们可以轻易发现RC滤波器在这种情况下是无效的。

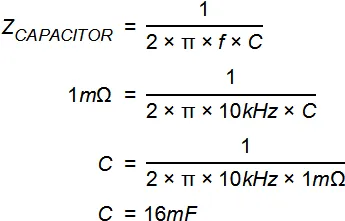

正如本系列文章中所述,我们只能在VRM控制环路带宽(BW)范围管理PI事件;通常这个带宽在100kHz范围内。举一个简单的例子,通过添加一个电容器,我们可以在10kHz时实现10mΩ的阻抗目标。

等式12-1

这不是错误。实际上,为了在10kHz时达到10mΩ这个看似轻松的目标,我们确实需要16毫法(mF)的电容。借助VRM环路增益,如等式9-1所示,我们可以使用实际可行的电容,并在正确使用VRM时达到目标。

12-1这个简单的等式揭示了一个与PI处理相关的重要事实:

随着我们所关注频率的降低,旁路噪声会变得越来越难处理。

当谈到“噪声”时,许多工程师会想到电磁干扰(EMI)或电磁兼容性(EMC)的讨论或标准中兆赫兹(MHz)到吉赫兹(GHz)范围内的噪声。这一范围内的噪声确实很难处理,处理千赫兹(kHz)或更低频率的噪声也同样困难,因为它对电容的需求是不切实际地巨大。值得一提的是,这正是许多音频爱好者一直在努力解决的频率范围。音频领域的许多降噪技术都适用于PI噪声,尤其是在我们的测量设置中。

等式12-1指的是输出电源轨噪声,但这一挑战普遍存在于所有的功率印刷电路板(PCB)上。例如,在我们的VRM系统中,需要在电压参考(VREF,或简称带隙参考)子模块中使用大量噪声旁路电容。要在目前PI项目中实现低噪声VREF,同样的等式表明,至少需要10nF(或10,000pF)的噪声旁路电容;其容量太大,无法集成到IC器件内部。这就是为什么许多高端LDO器件建议使用10nF左右的外部降噪电容。

电源完整性=各层面因的权衡

多年前,也就是在PI“运动”兴起之前,我写过一篇关于LDO噪声的应用笔记,对其进行了详细探讨。

在这篇论文中,我就如何最大限度地降低N型MOS-FET输出级LDO器件的输出噪声提出了见解。方法很简单:在其VREF和噪声增益级的正确位置增加噪声旁路电容。现在,凭借所有关于PI的知识,我想对过去的工作进行修正。

从PI中学到的最重要的一课,便是避免VRM在频域特性中出现任何峰值。

在此,我们希望获得:

平坦的输出阻抗/PDN阻抗 平坦的输出噪声密度 以及平坦的PSRR

每个VRM系统都是为其它负载设备供电而设计。因此,结合了多个VRM和负载的最终应用系统会表现出与这些因素相关的综合频域性能特征。每当我们在单个VRM特性分析结果中看到频域峰值时,这样的峰值可能会与其负载设备相互作用而产生更大的峰值,这被视为PI所面临的一项挑战。

回顾本系列文章——“哦,不!”,我确实引入了一个很大的噪声峰值。在撰写那篇文章时,我的初衷是将DUT在10Hz至100kHz频段内的均方根(RMS)噪声降至最低;但我也的确在500kHz处产生了尖锐的噪声峰值。

这又引出我们在PI实践中得到的另一个重要教训:

针对某个PI因素优化所做的任何努力,都是以牺牲一个或多个其它PI因素为代价的。

当您将某一参数调到最大时,就需要在另一方面付出代价。就我个人而言,我选择了10Hz至100kHz频段的最低RMS噪声,其代价是500kHz处的噪声峰值。

ZOUT与输出噪声间的紧密联系

在本文中,我们进行了两项测试来展示VRM输出阻抗ZOUT是如何形成其输出噪声的。

在典型的VRM器件中,我们有两到三级控制环路系统,其中最简单的是由一个VREF、一个误差放大器(EA)级和一个输出晶体管级组成的线性稳压器或LDO稳压器。相比之下,开关电源(SMPS = 开关稳压器)具有多个VREF、电压环路、电流环路和/或输出晶体管级。

随着这些级之间电气节点的连接,我们从上游级开始,以一个有限的热噪声量作为输出,而这种白噪声会与节点阻抗相互作用。为简单起见(因为这毕竟不是一篇学术论文),我们在这里只关注热噪声——如果完全没有电子电荷的移动,我们将观察到零噪声;相反,当我们观察到明显的噪声量时,必然存在一定量的电子运动。

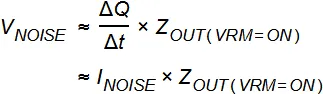

等式12-2

在等式12-2中,我们假设INOISE具有白噪声特性;即在很宽的频率范围内显示出非常平坦的功率。

还记得上面这个加粗字体的陈述吗?听起来是不是很熟悉?

在第10篇文章中,我们回顾了脉冲负载瞬态响应,其中脉冲在很宽的频率范围内具有平坦的功率。白噪声与脉冲之间的唯一区别是,白噪声在整个频率范围内具有完全随机的相位,而脉冲的相位则非常均匀。

除了VRM的直流偏置项VVRM外,等式12-2和等式10-2都表明,我们可以从噪声图中看出ZOUT(VRM=ON)的形状。

等式10-2

第10篇文章中的等式10-2

输出噪声实验测试#1:

N型MOS-FET输出级LDO

在适用的情况下,与P型稳压器相比,采用N型MOS-FET输出晶体管的线性稳压器是一个更好的选择;因为N型器件对电容性负载的敏感性较低。

然而当我们放置过多的电容时,N型LDO就会开始表现出对电容元件的敏感性。

N型稳压器稳健性的基本机制源于其作为电压跟随器/源跟随器/发射极跟随器的输出级。电压跟随器电路以其作为稳健电源模块的能力而知名;网上有很多信息告诉我们电压跟随器如何在过大的电容负载下开始表现出增益峰值。不过,这篇简短的技术博客简单明了地解释了我们需要知道的一切。

通过在各处放置电容器以增加噪声旁路,我们最终制作出一个良好的Colpitts振荡器。

尽管它没有发生振荡,但我之前的一个项目正是沿着这个方向进行的。

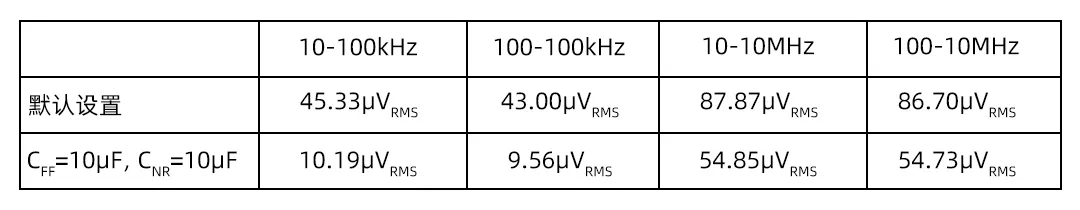

在第一次实验测试中,我们使用N型MOS-FET LDO评估板作为DUT,并按照以下2×2矩阵中详细描述的测试方法进行了总共四次测量。

结果如图12-2所示,其中第一(左)轴用实线表示输出噪声,第二(右)轴用虚线表示输出阻抗。我们有意调整了这两个坐标轴以叠加峰值。

图12-2,实验测试#1:N-FET LDO中ZOUT与输出噪声的关联性

在图12-2中我们可以清晰地看到,尽管在“默认设置”下没有看到峰值,但在CFF=10μF和CNR=10μF设置下,输出噪声谱密度和输出阻抗的两个图表中都出现了峰值。此外,我们还可以观察到,这些峰值的形状与等式12-2和等式10-2所描述的形状非常相似。

在RMS噪声表中,我们可以判定CFF=10μF和CNR=10μF的设置为整体上的最佳选择,但我们需要关注峰值是否会变得更高或更尖锐。随着峰值的增加,10Hz至10MHz或100Hz至10MHz范围内的RMS噪声值可能会超过“默认设置”下的值。

或者,如果您关注的噪声频率在1MHz附近,那么图12-2告诉您应该使用“默认设置”来避免峰值。

如您仔细查阅市场上许多“低噪声”VRM的数据手册,会发现这种高频峰值的存在。

输出噪声实验测试#2:

P型MOS-FET输出级LDO

在第二次实验测试中,我们使用了另一种具有P型输出晶体管的线性稳压器。

在PCB面积有限的应用中,许多工程师希望减少VRM输入和输出电容的数量,以低于供应商推荐的目标。最近,在为一个新项目构思创意时,我深入研究了这个问题并收集了相关数据。

其中,DUT是一个输入电压为5V、输出电流500mA的P型FET LDO。供应商推荐使用1μF的输出电容;但如果可能的话,我们希望使用更小的电容器来节省PCB面积。

因此,与实验测试#1一样,我测试了1μF(默认)、0.33μF和0.1μF三种不同电容值下的输出谱密度与输出阻抗。

所有P型LDO的第一个极点都是由输出电容COUT和输出节点的组合阻抗(包括负载阻抗、P型FET的导通阻抗,以及连接到输出节点的所有元件)配对而成。当我们减小输出电容COUT时,这个极点会向更高的频率移动,从而自动扩展其控制环路带宽,但相位裕度会变差。

图12-3展示了测试结果,其中第一(左)轴用实线表示输出噪声,第二(右)轴用虚线表示输出阻抗。同样,这两个坐标轴经过有意调整,以叠加峰值。

图12-3,实验测试#2:P-FET LDO中ZOUT与输出噪声的关联性

以下为主要观察结果:

与实验测试#1一样,噪声密度和输出阻抗的曲线形状非常相似,且峰值位置相匹配。 在测试过程中,我们确认所有三种情况均未发生自振荡。 然而,当使用0.1μF的电容时,在输出阻抗测量过程中注入扰动信号后,观察到了受迫振荡。 由于此类受迫振荡,蓝色虚线表示的输出阻抗曲线出现了非常难看的峰值。根据对应的噪声峰值判断,其真正的ZOUT峰值在6MHz至7MHz之间。 引用之前关于第一极点如何移动的解释,我们可以观察到ZOUT峰值向更高频率移动并变得更加尖锐。这表明环路带宽扩展,相位裕度减小。⇒ 请参阅《ZOUT到NISM:输出阻抗到非侵入式稳定性测量》的相关内容;我们在其中回顾了ZOUT如何作为控制环路传递函数的直接测量指标和指示器。 除了6MHz时的受迫振荡外,0.1μF的电容设置相较于其它两条曲线显示出更高的值,并且在低频区域呈现约50mΩ的平坦ZOUT。这表明其VRM控制环路未起作用,也表明该设置无法使用。 遵循VRM供应商的建议用法是明智之举。

文章来源:Qorvo半导体