作者简介

本文是第二届电力电子科普征文大赛的获奖作品,来自上海科技大学刘赜源的投稿。

平面磁集成技术的发展

在此基础上,平面磁集成技术开始广泛应用于高功率密度场景,通过将变压器的绕组(winding)设计在pcb电路板上从而代替利兹线,从而极大降低了变压器的高度。

然而pcb的铜带厚度并不大,一般不会超过4oz(140μm),因此想要通过pcb传输大电流会有极大的损耗。为了降低这部分的损耗,有人可能会想到只要增加铜带宽度,问题就可以迎刃而解。然而这种方式变相地增加了变压器占据的面积,同时会让磁芯体积更加庞大。

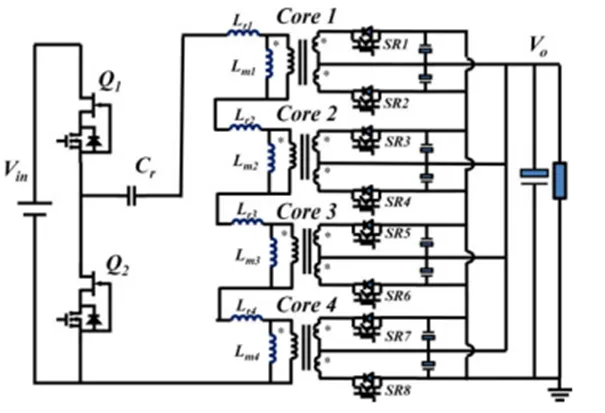

那么到底如何解决这一问题呢?由于副边的输出电流极大,因此在实际应用中副边会被拆分成多个并联的状态,如图五所示,此时每一路的输出电流仅为总电流的1/4。

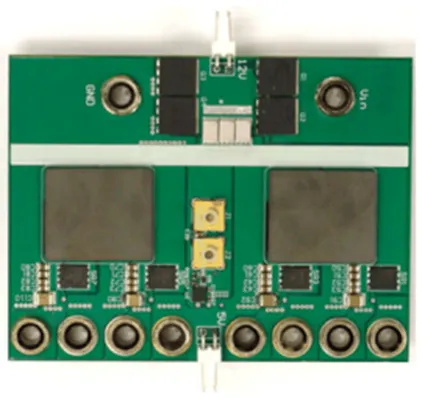

根据功率计算公式,损耗功率与电流成二次方关系,因此此时副边的损耗只有原本的1/4。随着器件的发展以及第三代半导体(GaN, SiC)的推广,此时工作频率提升到了1MHz,更加有效地减小了整个电路的体积。图六显示了平面变压器下的LLC电路,此时功率密度提升到了700W/in³[1]。

图五:ISOP 4相LLC电路

图六:4相LLC电路板

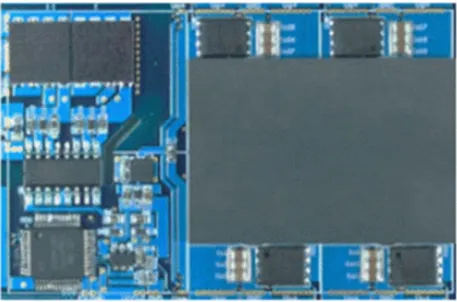

在这之后的发展就顺理成章起来了,两个变压器导致整体电路面积的增加,因此将2个变压器集成到1个磁芯上就可以有效提升功率密度。集成之后的电路板如图七所示,此时电路的功率密度已经突破了900W/in³[2]。

图七:4相单变压器LLC电路板

来自器件的制约

此时针对电路方面的优化已经十分有限了,可能的优化方向就是这个巨大的矩阵变压器(matrix transformer)。变压器占据了整个电路一半的体积,因此出现了新一类的开关电容电路(Switched Capacitor Converter)。但是,LLC仍然凭借其极高的效率与功率密度,简单的拓扑结构以及变压器提供的输入输出隔离成为当下的主流应用电路。 随着器件的发展,LLC电路功率密度也在不断更新。在当下的数据中心供电场景中,LLC电路已经可以达到超过3kW/in³的惊人的功率密度,当下能够限制电路体积减小的就是来自器件与材料的制约。

总结

除了集成电路,电力电子领域也在经历着类似于“摩尔定律”的发展趋势,即每隔一段时间,电路的功率密度就会有一次质的飞跃。尽管当前电路的功率密度已经达到了一个相对较高的水平,但在未来,随着半导体和磁性材料的不断进步,我们有望见证电路功率密度的再次提升。这些新材料和技术的出现,将为电力电子领域带来前所未有的机遇和挑战。

参考资料

[1] D. Huang, S. Ji and F. C. Lee, "LLC Resonant Converter With Matrix Transformer," in IEEE Transactions on Power Electronics, vol. 29, no. 8, pp. 4339-4347, Aug. 2014.

[2] C. Fei, F. C. Lee and Q. Li, "A new design paradigm for GaN based LLC converter," 2017 IEEE Southern Power Electronics Conference (SPEC), Puerto Varas, Chile, 2017, pp. 1-6.

文章来源:英飞凌工业半导体