作者:Zachariah Peterson

高层数 PCB 的布线策略丰富多样,具体取决于 PCB 的功能。这类电路板可能涉及多种不同类型的信号,从低速数字接口到具有不同信号完整性要求的多个高速数字接口。从布线规划和为各接口分配信号层的角度来看,这无疑是一项极具挑战性的任务。

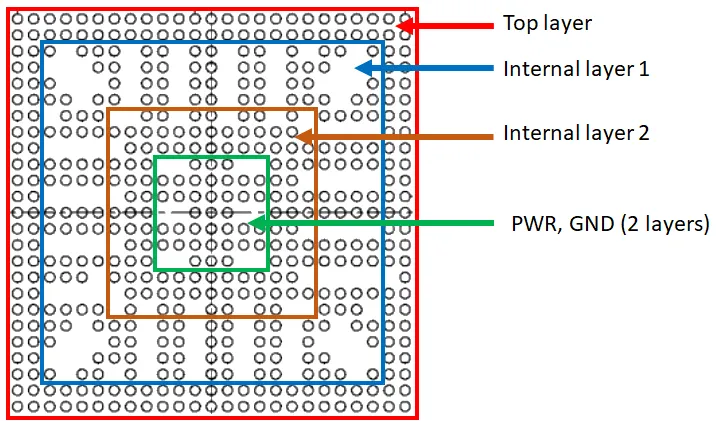

提及高层数 PCB 的布线策略,就不得不谈到众多BGA封装的引脚布局设计。高引脚数 BGA 通常包含多种不同的数字接口,尤其是当元件为典型的微处理器或FPGA时。这是导致 PCB 层数增加的最常见因素之一。

由于高层数设计中往往同时面临多个挑战,本文将逐一解析这些挑战,并分享能够成功实现高层数 PCB 布线的实用策略。

是什么导致 PCB 层数增加?

许多设计师都能熟悉估算 BGA 引脚全连接所需层数的简单公式。当 BGA 的焊球间距足够大(允许在引脚间布线)时,每层信号层可容纳两行 BGA 引脚:

当元件引脚间距极细(BGA 焊盘间无法布线)时,所需层数需翻倍;若大量引脚为电源和接地引脚,层数则会减少。此外,大量四方扁平封装(Quad 封装)也可能导致高层数需求,但其引脚数通常远低于中等尺寸 BGA(高端 Quad 封装约有几百个引脚,而中等 BGA 引脚数更高)。

四大核心布线策略

策略 1:“无策略”

“无策略” 策略是迄今为止最简单的方法,其核心是在确保可布线性的同时尽量减少层数。具体实施方式包括:选择所需层数并通过标准扇出方法从 BGA 布线、采用固定层数紧凑排布所有走线,或自由布线并根据需求添加新信号层。该策略适用于以下场景:

无需按阻抗规格将不同信号分隔到不同层

所有接口均无阻抗要求(如串行外设接口 SPI)

所有接口的阻抗要求一致

有阻抗规格要求的接口数量极少(如 1-2 个)

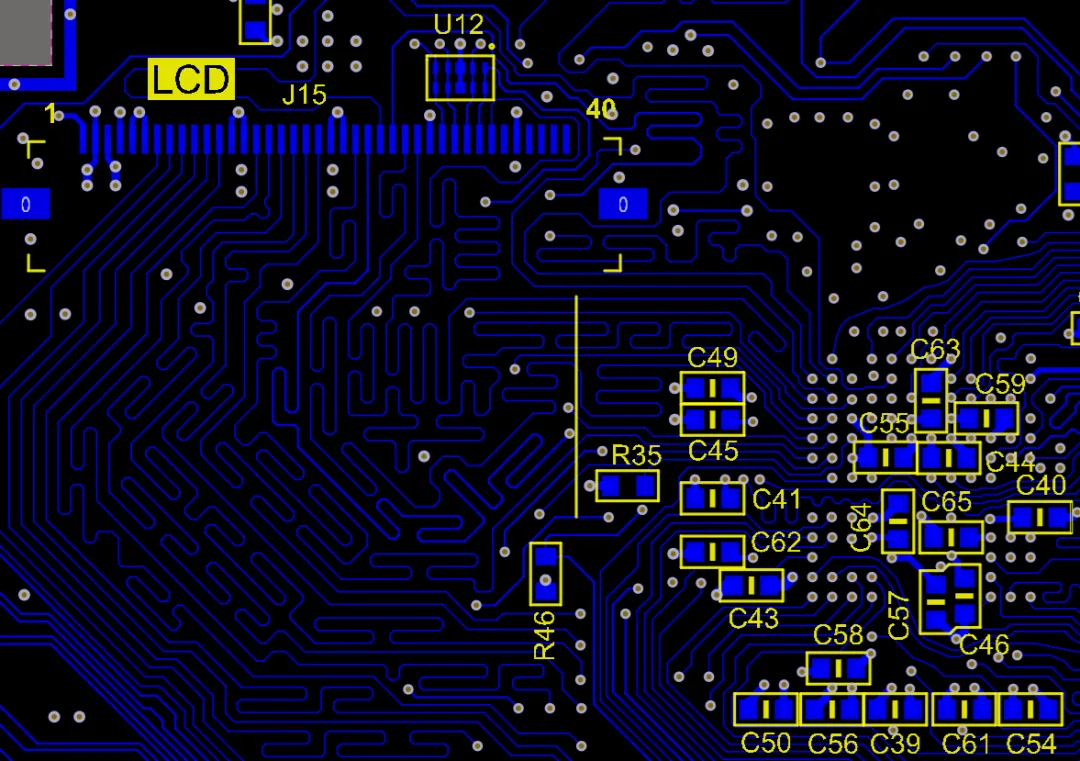

示例:该并行接口从 BGA(右下角)起始布线,连接至外接 LCD 模块(左上角)。

策略 2:按接口优先级分配层

在此策略中,特定的阻抗受控接口会被分配专属的信号层,并且主要在这些层内进行布线。制造商随后采用阻抗控制方法,确定构建电路板层叠结构时使用的电气特性。当存在多个需要阻抗控制且可能具有不同目标阻抗值的高速接口时,可采用这种策略。对于部分差分接口,尽管其标称阻抗目标相同,但带宽需求可能不同,这就需要为不同接口设置不同的线宽和间距。

DDR4

CSI-2

1 Gbps LVDS

10 Gbps 以太网

具体可见下方图表中这些接口如何被分配到不同层中。

策略 3:高速层与低速层分离

此策略适用于需要阻抗控制的接口数量较少,或所有阻抗受控接口具有相同阻抗要求的场景。通过将信号分隔到专用的高速层和低速层,可实现更清晰的分层设计。这类似于在六层板中设置四个信号层,将低速信号层相邻放置的做法。

这种策略适合采用正交布线(相邻层信号走向垂直),尤其当低速信号分布在相邻层时效果更佳。例如,下方示例中的布线在两个不同层上的元件之间采用正交走向:

策略 4:电源与信号共层设计

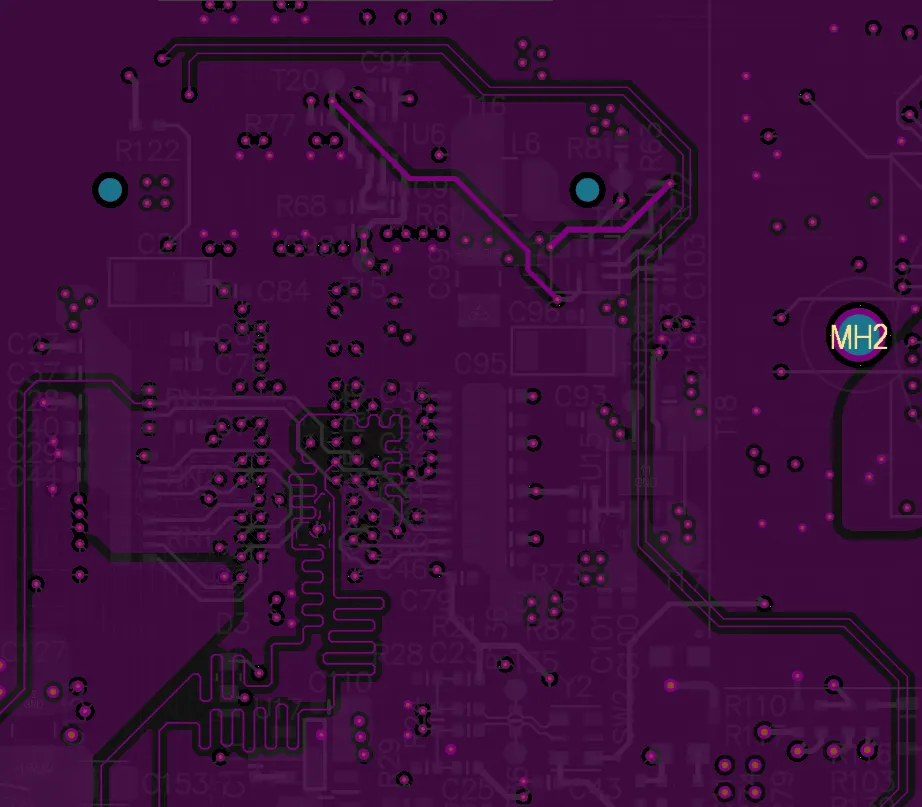

在高层数电路板设计中,我经常采用的另一种布线策略是将部分信号与电源铺铜整合到同一层。

在绘制了电源铺铜的层中,允许布置信号走线,尤其是低速信号或配置信号。如下图所示的示例布线:

只要保持足够间距,在电源层布线是可行的。

无论是制造电力电子设备,还是应对跨领域协作挑战,Altium Designer® 的全套 PCB 设计功能与 Altium 365™ 平台都能轻松满足需求,支持设计数据无缝共享与生产流程高效推进。这仅仅是 Altium 解决方案的一小部分,立即免费试用 Altium Designer + Altium 365,探索高层数 PCB 设计的无限可能!

文章来源:Altium