本文旨在解决DC-DC开关稳压器的功率级设计中面临的复杂难题,重点关注功率晶体管和自举电容。降压转换器用于演示忽视功率晶体管时序规范的影响,以及移除自举电容时会发生什么情况。功率晶体管具有最小导通和关断时间要求,以确保FET栅极电容正确充电和放电,从而保证晶体管完全导通和关断。如果忽略这些要求(例如为了获得更快的开关速度),就会出现输出不稳定和开关频率错乱等问题。此外,自举电容对于维持这些晶体管的运行至关重要,若没有自举电容,晶体管就不会有足够的驱动强度,导致无法完全导通。

什么是自举电容?

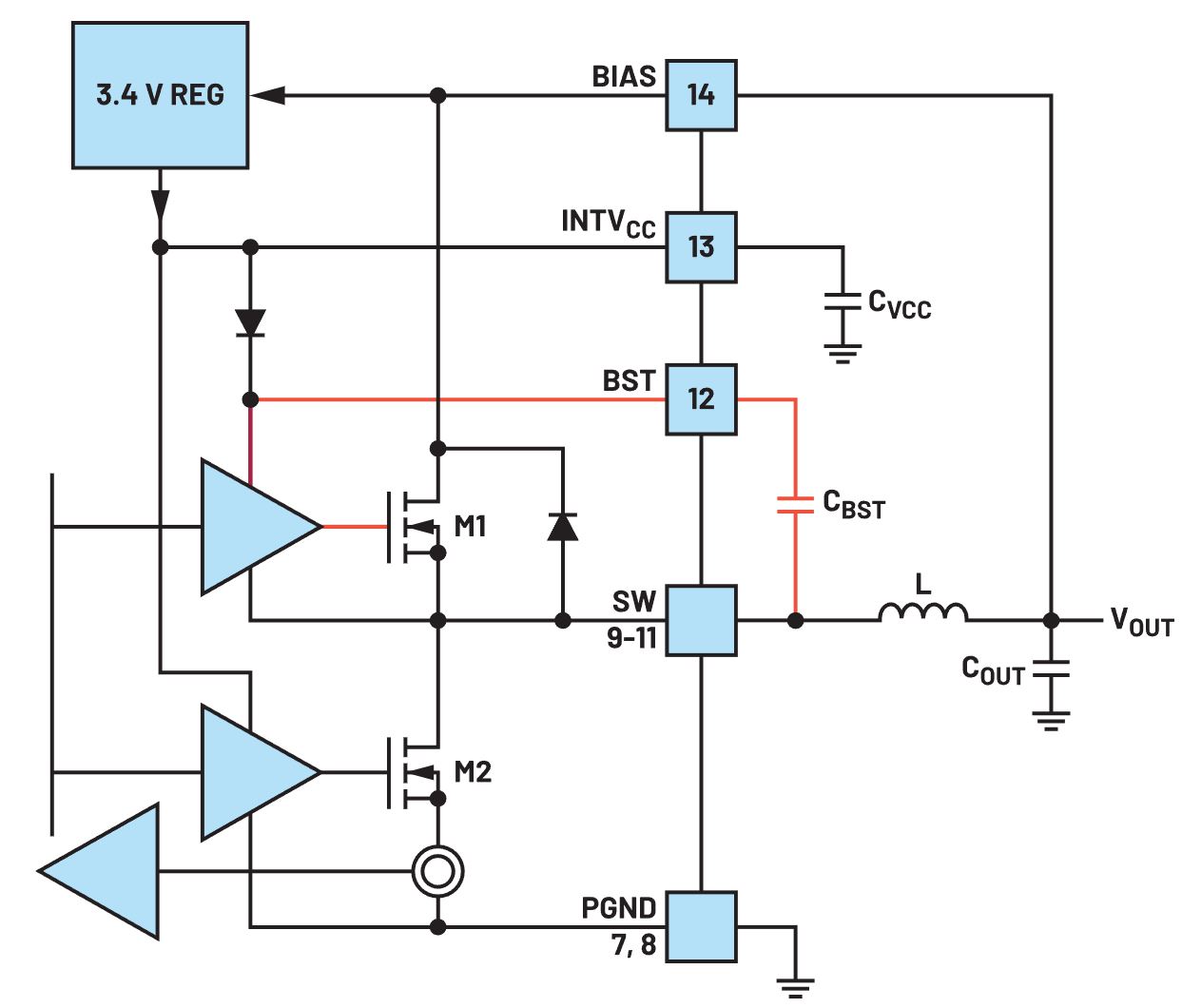

自举电容负责维持顶部N沟道MOSFET正常运行。图1的橙色高亮部分显示了这一点。

图1.LT8610数据手册中展示自举电容功能的框图。

当顶部N沟道MOSFET闭合时,开关节点的电位与输入源大致相同。这意味着顶部MOSFET的源极电压高于栅极电压(来自栅极驱动器)。若没有高于NMOS阈值电压的正栅源电压,MOSFET将无法导通。因此,需要使用自举电容来确保栅极电压始终高于源极电压。

忽略自举电容

省略自举电容不会给设计人员带来什么明显的好处,这样做可能是为了缩减BOM尺寸和成本,或者仅仅是忘记包含这些元件。然而,此决定会带来负面影响,因为要帮助芯片为顶部FET的栅极提供足够的电压以使其完全导通,自举电容是必不可少的,如图2所示。

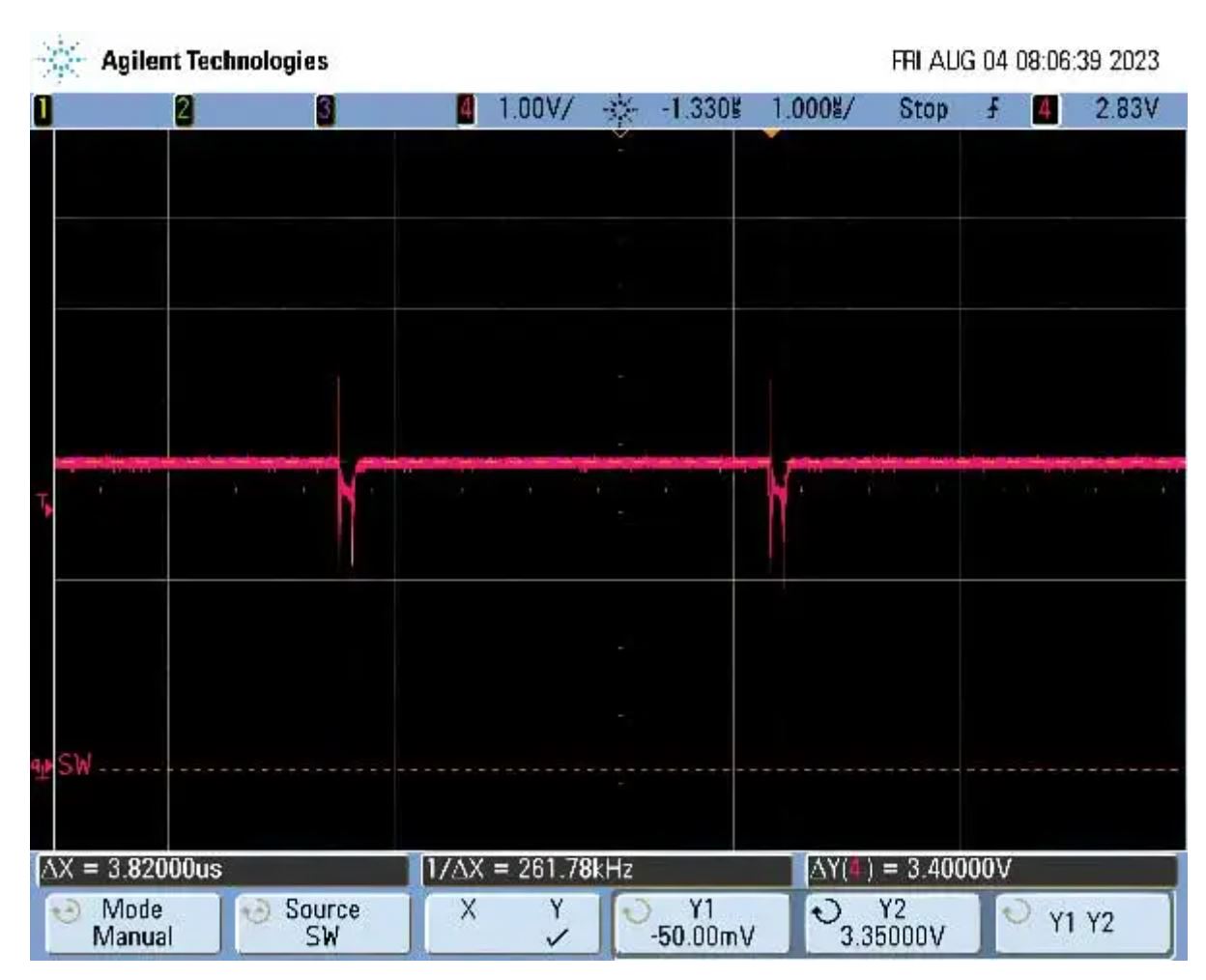

图2.无自举电容的开关节点。

如果顶部FET未完全导通,器件将无法调节输出电压。FET将在线性区域内工作,消耗大量功率并使芯片升温。

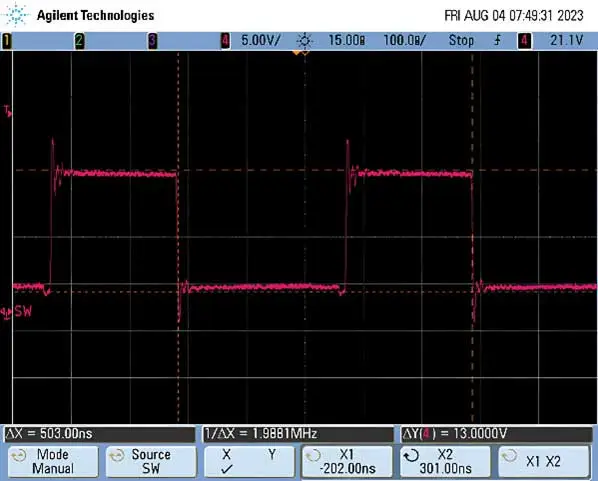

为了解决这个问题,设计人员必须添加自举电容。设计人员如果不确定要添加多大的电容,则应在数据手册示例中选择一个最接近其应用的值。如果器件需要自举电容,忘记添加该电容将导致SMPS故障。添加自举电容将能让顶部栅极驱动器有足够的驱动强度来操作处于饱和区的FET,使其充当开关,并向SW节点提供全部输入电压。这一点可以从图3中看出。

图3.带自举电容的开关节点。

违反最小导通时间规范

设计人员常常选择较高的开关频率以减小电路板尺寸,但由于开关损耗增加,能效比会降低。然而,当器件具有高频率和高降压比时,占空比会被迫变小,并可能降至最小占空比值以下。最小占空比如公式1所示。

其中,tmin-on定义为电感由输入源充电的最短时间。开关转换器具有规定的最小导通时间值,设计人员必须遵守该值以确保FET正常运行(因为FET无法瞬间完成切换)。设计人员可以自由选择开关频率。然而,当指定的开关频率过高以及降压比过大时,导通时间就会被迫低于最小值。

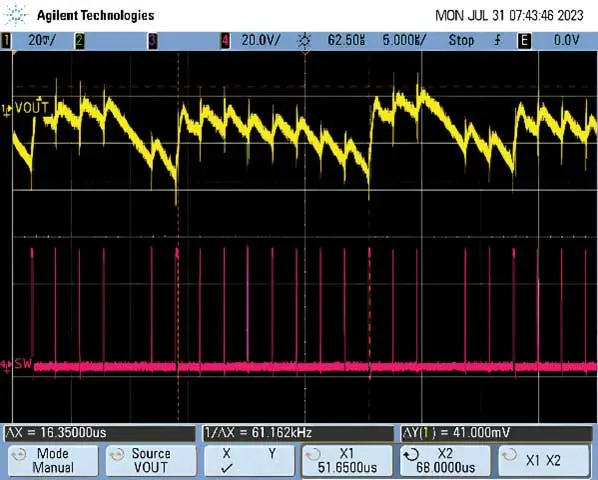

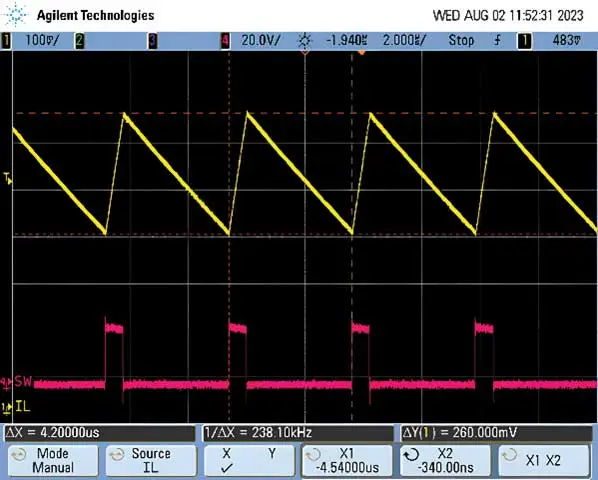

当导通时间被迫低于其最小值时,电感电流在一个周期内的放电速度将比充电速度更快。当新的周期开始时,起点将低于前几个周期的起点,这种现象被称为电流降。最终,电流和输出电压都会下降到很低的程度,以至于器件内部产生更大的占空比(具有更长的导通时间)来调节输出电压,如图4所示。

图4.违反最小导通时间的电流波形。

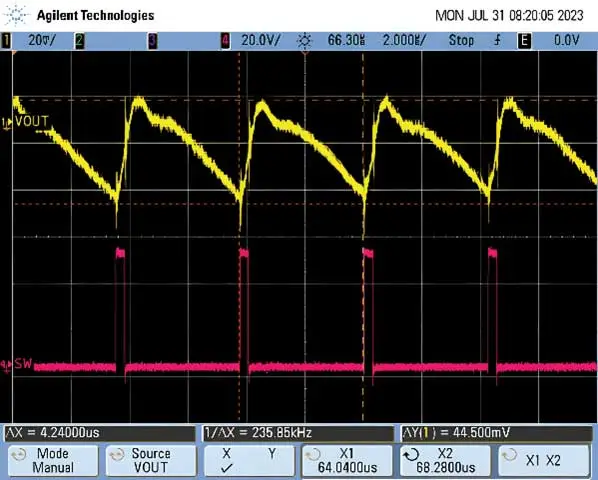

电感电流纹波的下降也会在转换器的输出电压中表现出来。输出电压纹波变得更加嘈杂,这可能会影响敏感负载并降低EMI性能。此影响可以从图5中看出。

图5.违反最小导通时间的输出波形。

这个问题有一个简单的解决办法。导通时间主要受开关频率影响,因此设计人员可以通过降低频率来解决该问题。但这样做的代价是需要更大的功率级元件,主要是更大的电感。降压转换器的功能改进体现在周期间一致的导通时间,以及图6中稳定的电流纹波和图7中稳定的输出纹波。

图6.稳定的电流纹波

图7.稳定的输出纹波。

违反最小关断时间规范

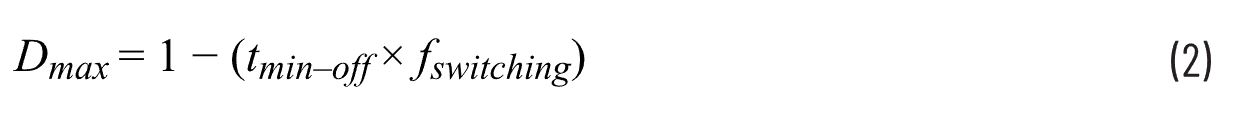

某些应用可能需要较小的降压比,这可能会违反转换器的最小关断时间规范。tmin-off是tmin-on的补充,定义为电感未由输入源充电的最短时间。与导通时间要求类似,SMPS必须关断规定的时间以确保FET正常运行(允许正常放电)。当要求的占空比大于允许的最大占空比(由式2给出)时,就会违反最小关断时间规范。

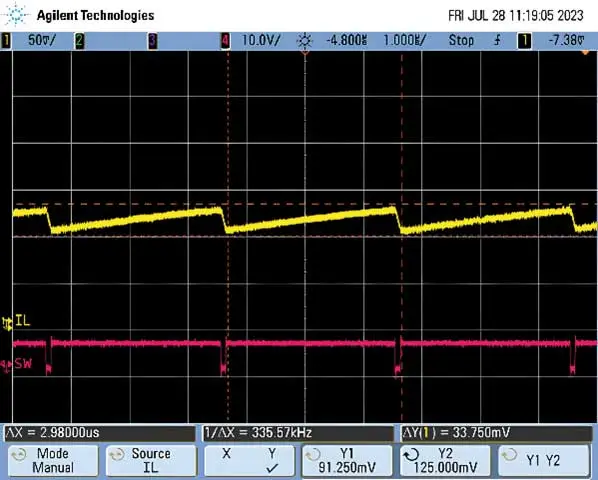

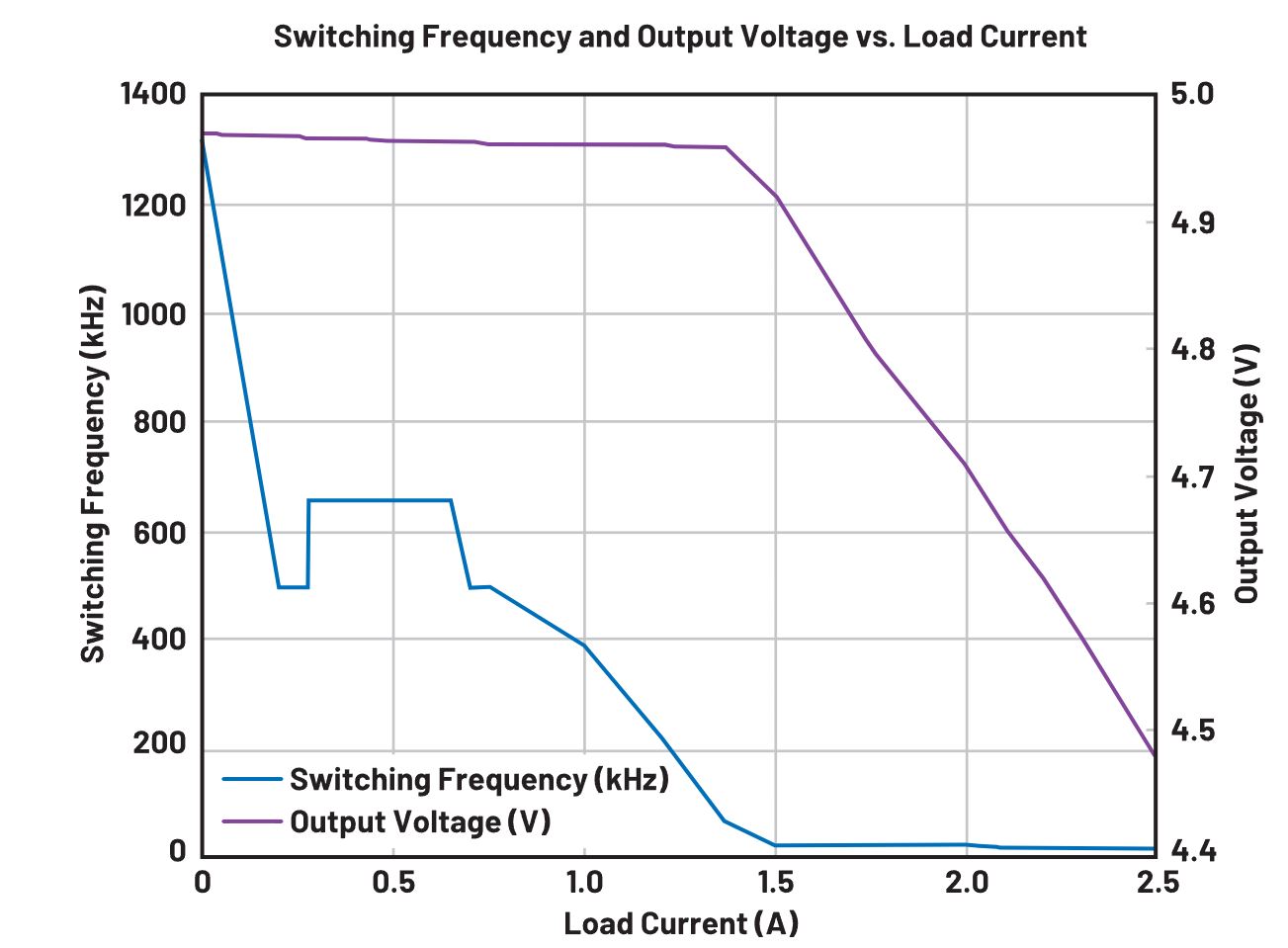

如果占空比超过最大值,SMPS将折返其配置的频率,以避免违反最小关断时间规范。这一点可以从图8中看出。器件最初配置为2MHz频率。

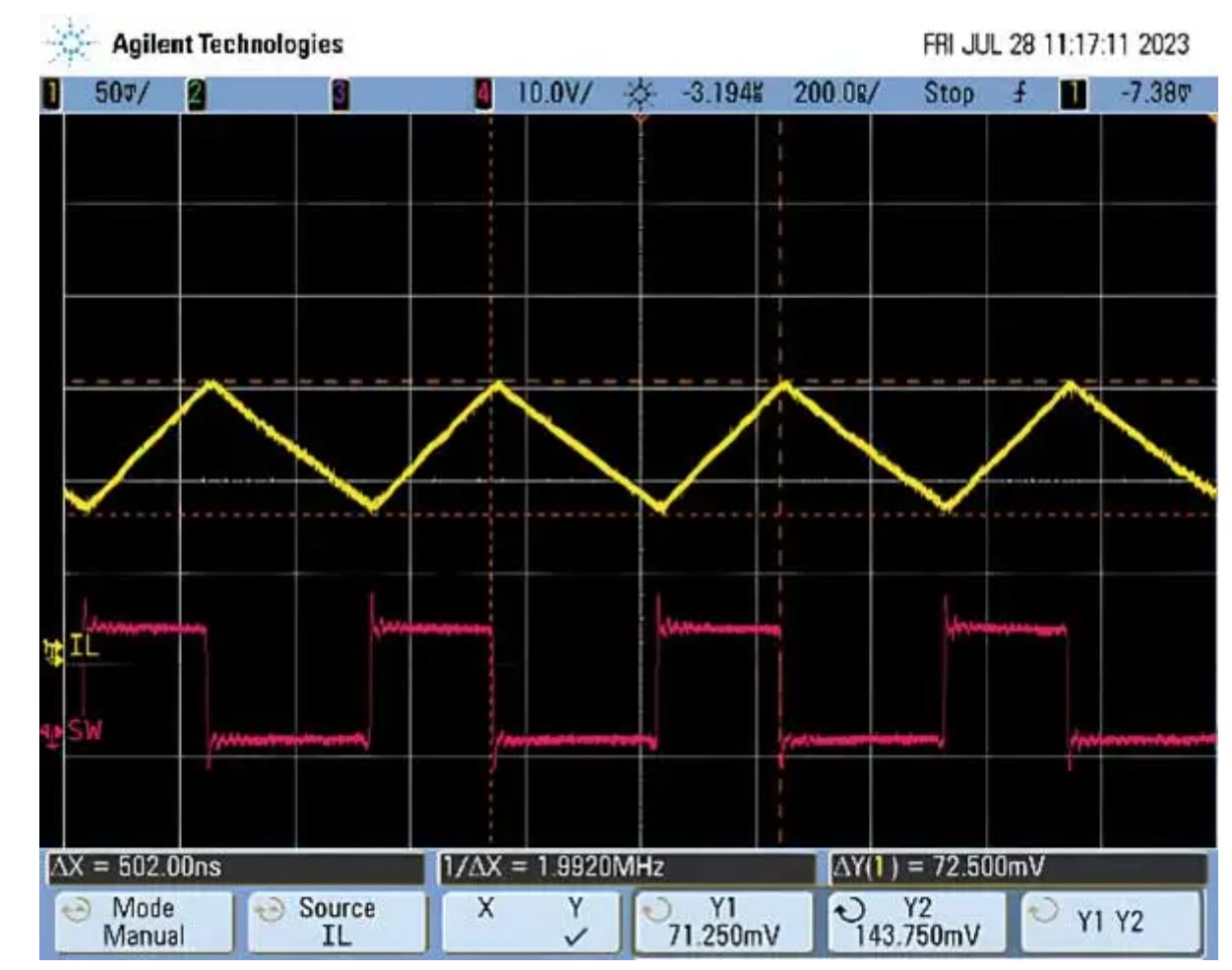

图8.违反最小关断时间的电流波形。频率折返至335kHz。

在图9中可以看到,随着负载增加,器件频率会折返以保持恒定的输出电压。器件在DCM下运行至约0.28A,这就是频率下降到约495kHz然后又回升至657kHz的原因。以657kHz的频率运行时,器件可以保持正常操作,直至负载达到0.7A。此时频率降低以保持适当的输出电压,直至负载达到1.4A左右。发生这种情况时,器件无法在保持输出电压的同时将频率降低到100kHz以下(该器件指定的最低反馈频率),因此输出电压开始下降。

图9.负载调整和折返频率。随着负载增大,频率会折返以维持稳定的输出电压。

在图9中可以看到,随着负载增加,器件频率会折返以保持恒定的输出电压。器件在DCM下运行至约0.28A,这就是频率下降到约495kHz然后又回升至657kHz的原因。以657kHz的频率运行时,器件可以保持正常操作,直至负载达到0.7A。此时频率降低以保持适当的输出电压,直至负载达到1.4A左右。发生这种情况时,器件无法在保持输出电压的同时将频率降低到100kHz以下(该器件指定的最低反馈频率),因此输出电压开始下降。

这个问题的解决办法不像违反最小导通时间规范那么简单。设计人员通常需要满足特定的输入电压和输出电压要求,因此无法随意更改占空比来延长关断时间。如果设计人员可以提供更大的输入电压,则器件将以设定的频率工作,因为较小占空比会防止器件违反最小关断时间规范。这一点可以从图10中看出,其中器件以设定的2MHz频率运行。

图10.未违反最小关断时间的电流波形。设定频率为2MHz。

与最小导通时间相反,降低频率只会在一定负载以下起作用。如果设计人员不能充分降低开关频率以避免违反最小关断时间规范,那么理想的做法是选择另一种能够处理更高占空比和更短导通时间的器件。

结论

本文重点讨论如何让功率晶体管保持正常运行。占空比要求过高或过低都会使开关转换器不稳定,进而造成不良后果,例如开关频率降低、输出电压不稳定以及电感在电流方面的性能不良等。此外,忽略自举电容不仅会妨碍晶体管正常工作,还可能对负载、晶体管或芯片本身造成严重后果。

文章来源:亚德诺半导体