圣邦微电子推出 SGM48211 系列 120V 高压半桥栅极驱动产品。器件可应用于电信,数据通信,便携式存储的 48V 或更低电压系统中的电源转换器,半桥、全桥、推挽、同步降压,正激变换器和同步整流器等方面。

一颗好的高压半桥栅极驱动芯片需要具备怎样的性能?提供 4A 拉电流和 4A 灌电流输出能力;能够以最小的开关损耗驱动大功率 MOSFET;电源引脚 VDD 运行范围 8V 至 17V(绝对最大值 20V);输入引脚耐压为 -10V 至 20V;强鲁棒性;高侧、低侧两个通道完全独立,且彼此的导通和关断之间存在 2.5ns(TYP)延迟匹配;驱动器内部具备欠压锁定保护功能防止故障;HS 引脚抗负压能力强,支持 100ns -(24V-VDD) 负压和 50V/ns dV/dt 强抗噪声能力;内置自举二极管……SGM48211 就是一个集合以上全部性能的绝佳选择。

SGM48211 的 HS 引脚具有抗负压噪声能力,在 100ns 时间内可承受的最大负压是 -(24V-VDD)。当 HS 引脚负压不超过芯片绝对最大额定值,芯片输出正常(如图 1 所示)。

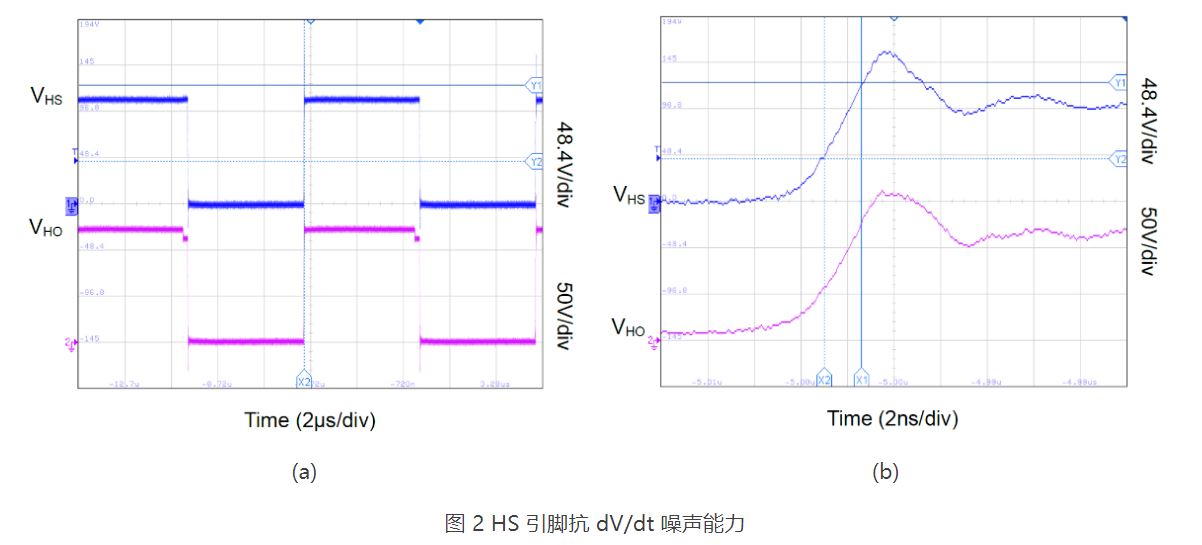

SGM48211 的 HS 引脚抗 dV/dt 噪声能力达到50V/ns。当 HS 引脚电压变化速率在芯片绝对最大额定值范围内,芯片正常工作,HO 和 LO 输出正常(如图 2 所示)。

图 2 HS 引脚抗 dV/dt 噪声能力

SGM48211 内部集成 120V 额定电压的自举二极管,可以帮助客户省却二极管电路设计并减小 PCB 尺寸。如图 3 所示,当上管 Q1 关断,下管 Q2 导通时,HS 引脚电压低于电源电压 VDD,VDD 通过自举二极管 DBOOT 对自举电容 CBOOT 进行充电,在自举电容两端产生 VBS 电压;当下管 Q2 关断,上管 Q1 开通时,驱动芯片内部上管 MOS 导通,由自举电容两端悬浮电压 VBS 支持 HO 相对 HS 的开关。随着上管 Q1 导通,HS 高压时自举二极管处于反偏,VBS 和电源 VDD 被隔离开。

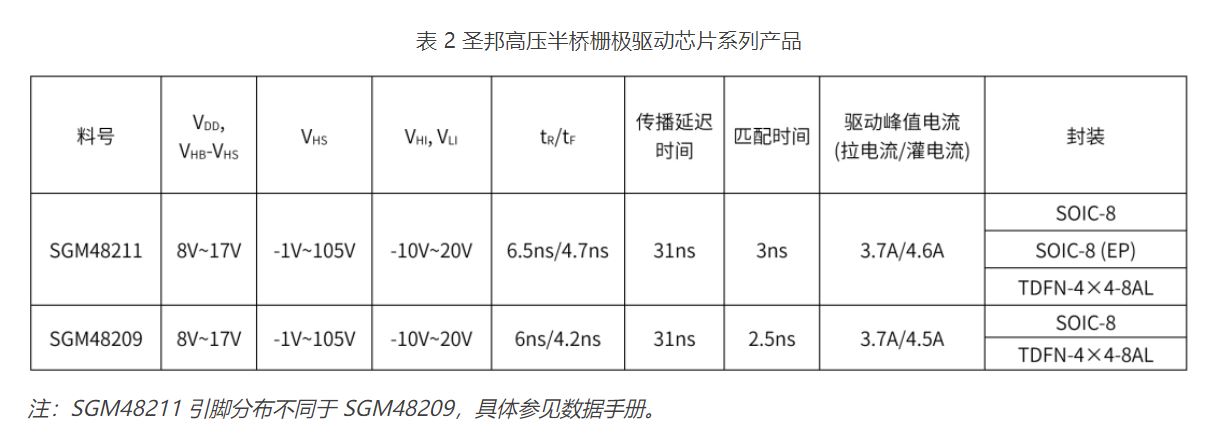

除 SGM48211 之外,圣邦微电子还推出了同系列 120V 高压半桥栅极驱动芯片 SGM48209 可供客户选择,其典型特性如表 2 所示。

接下来,我们将以 SGM48211 为例,探讨一下在使用高压半桥栅极驱动产品过程中会遇到的各类问题及应对方案。

首先,在电路设计之初,需要特别注意的是自举电容 CBOOT 的选取,不能过小,亦不能过大。

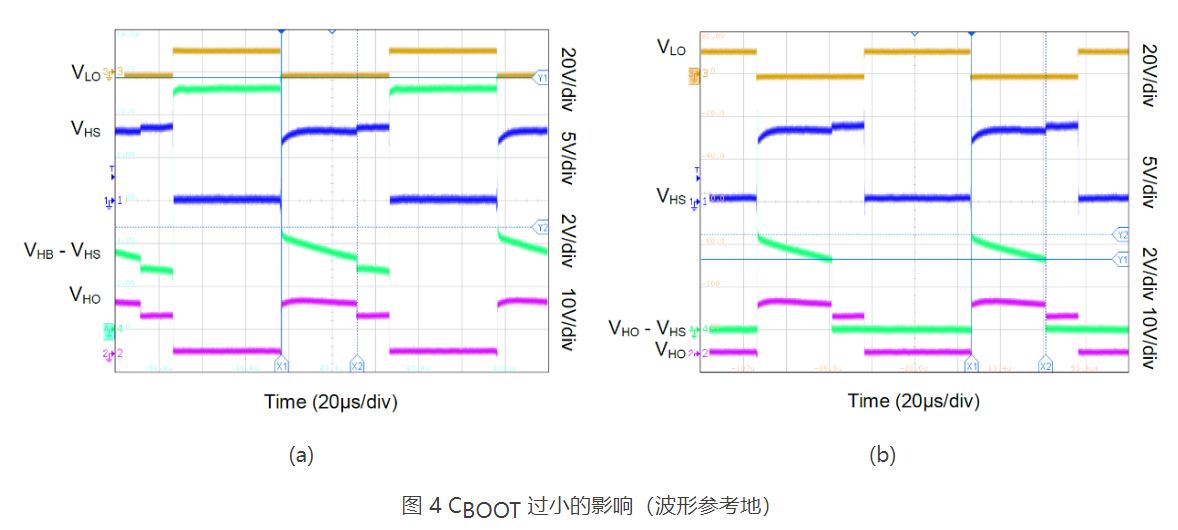

当下管 Q2 导通,HS 电压低于电源电压 VDD,自举电容 CBOOT 会被充电。自举电容仅在上管 Q1 开通时放电,给高端电路提供电源 VBS。选取 CBOOT,首先要考虑的参数是上管 Q1 开通时,自举电容允许的最大电压降。如果 CBOOT 容值选择过小,会出现如图 4 所示的现象,由于 CBOOT 上存储的电荷不足,VHB-VHS 的电压跌落至低于驱动芯片 HB 的 UVLO 阈值,从而触发驱动芯片欠压锁定保护,导致 HO 无输出,上管 Q1 无法开通。

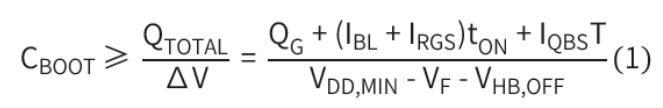

根据驱动芯片 HB 的 UVLO 值,可由式(1)求得 CBOOT 的最小值。

式中,QG 是功率管的栅极总电荷量;IBL 是 HB 对地漏电流;IRGS 是流入栅极-源极电阻器的电流;IQBS 是 HB 至 HS 静态电流;tON 是上管 Q1 导通时间;VF 是自举二极管 DBOOT 的正向导通压降;VHB,OFF 是驱动芯片 VHB 的下降 UVLO 阈值。

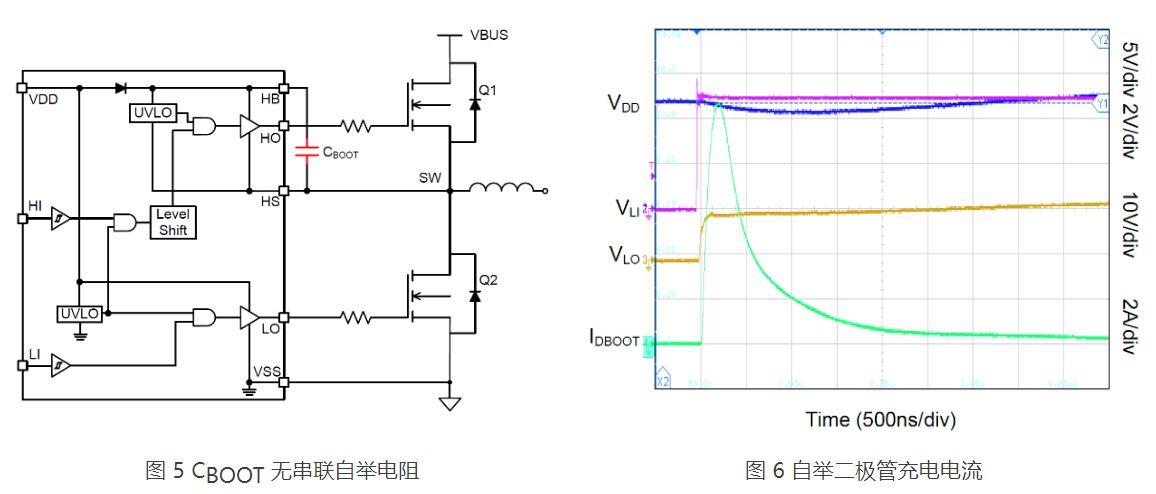

从式(1)可见,随着 QG 增大,自举电容 CBOOT 的取值也需要增大,CBOOT 增大会导致自举二极管瞬时充电电流增大。需要特别注意的是,由于自举二极管是集成在 SGM48211 的内部,集成的自举二极管的 Die 面积有限,散热能力有限。CBOOT 充电电流超出自举二极管散热能力时,可能会烧毁自举二极管。图 5、6 所示为在 VDD = 12V 条件下对 SGM48211 内部自举二极管充电时的峰值电流波形:CBOOT = 680nF,DBOOT 峰值电流为 10.7A。

可见,CBOOT 的容值如果选择过大,会导致自举二极管存在损坏的风险。实际应用中,由于功率管 QG 较大,CBOOT 取值不得不大时(如 CBOOT ≥ 680nF 时),为了保护 SGM48211 内部自举二极管,可以选择在 CBOOT 处串联一个自举电阻 RBOOT(典型值 1Ω 至 10Ω)来限制自举电容的充电电流(如图 7 所示)。如图 8 所示,在VDD = 12V,CBOOT = 680nF,RBOOT = 1Ω 条件下对 SGM48211 内部自举二极管耐峰值电流能力进行测试,结果与图 6 对比,DBOOT 峰值电流从 10.7A 降至 5.5A。

但是,自举电阻不可过大,否则会增加 VBS 时间常数。下管 Q2 的最低导通时间,即给自举电容充电或刷新电荷的时间,必须匹配这个时间常数。该时间常数取决于自举电阻,自举电容和开关器件的占空比,可由下式(2)求得。

式中,RBOOT 是自举电阻;CBOOT 是自举电容;D 是占空比。

当 CBOOT 串联自举电阻,需要考虑自举电阻带来的一个额外的电压降。

式中:ICHARGE 是自举电容充电电流;tCHARGE 是自举电容充电时间,即下管 Q2 导通时间;RBOOT 是自举电阻。

除了上述自举电容 CBOOT 的选取需要特别注意之外,高压半桥栅极驱动产品在实际应用中还经常遇到的一大挑战是 HS 引脚负压带来的芯片失效。

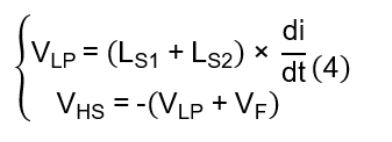

如图 9 所示,由于实际电路中存在上下管功率器件的封装电感和电路板走线的寄生电感,上管 Q1 导通时,电流经过上管流过负载电感;上管 Q1 关断换流时,续流电流经过下管 Q2 的体二极管流过负载电感,该电流会在 LS1、LS2 等寄生电感上产生电压,从而导致 HS 引脚处产生低于地线电压的负压。该负电压的大小正比于寄生电感的大小和开关器件的电流关断速度 di/dt,如式(4)所示,其中 di/dt 由栅极驱动电阻 RG 和开关器件的输入电容 CISS 决定。

式中,VF 是下管 Q2 的体二极管正向导通压降。

SGM48211 的 HS 引脚在 100ns 时间内可承受的最大负压是 -(24V-VDD),当 HS 引脚负压幅值超过驱动芯片 HS 引脚的耐负压最大值,可能会导致驱动芯片发生闩锁效应,产生不可预测的结果。如 HI 为低电平时,HO 从低电平跳到高电平,半桥两个功率管发生直通短路。如图 10、11 所示,在上管关断的时候 HS 引脚的瞬间电压达到了 -18.6V,这个负压使得 HO 从低电平跳变成高电平,上管和下管直通短路。

另外,自举电容两端最大的电压 VHB-VHS 等于 VDD-VF-VHS,HS 引脚负压过大可能会使自举电容处于过压状态,会有打坏电容,短路到 HS 的风险。同时如果 VHB-VHS 超过驱动芯片的绝对最大额定值,会导致驱动芯片过压损坏。

由上述分析可知,HS 引脚负压过大容易导致驱动芯片失效。因此,如何抑制 HS 负压,将是高压半桥栅极驱动芯片应用中的重要课题。为了减小 HS 引脚负压,在电路设计中需要注意:

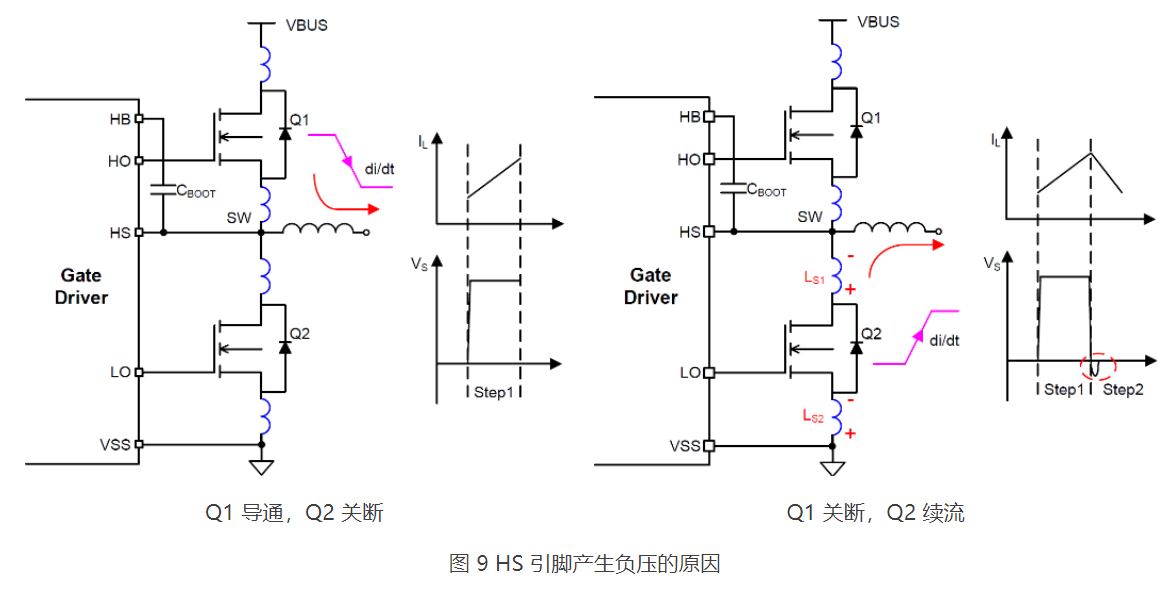

1、 优化布局,减少寄生电感(如图 12 所示)。半桥电路的两个功率管尽可能靠近放置,它们之间连线尽可能短粗;驱动芯片尽量靠近功率管,减少驱动回路的走线;使用低寄生电感的驱动电阻;使用低寄生电感的瓷片电容作为自举电容 CBOOT,同时 CBOOT 尽量靠近驱动芯片引脚;退耦电容尽量靠近驱动芯片引脚。

2、 降低功率管的开关速度,从而降低开关时的电流变化率 di/dt。增大驱动电阻(注意:这种方法会增加功率管开关损耗);外加缓冲电路。

3、 在 HS 和 VSS 之间增加一个低正向导通压降的肖特基二极管:快速将 HS 引脚负压钳位到 -0.7V 左右(如图 13 所示)。为验证该方法,在图 11 测试条件的基础上,增加 HS 到 VSS 的钳位肖特基二极管。上电测试后发现 HS 引脚负压被成功钳位,HO 输出无异常跳变,驱动芯片工作正常(如图 14 所示)。

4、 可以考虑在 HS 与 SW 间放置一个低阻值噪声抑制电阻 RVS。既可以作为驱动电阻起到限制上管 Q1 的开通速度和关断速度的作用,也可以作为自举电阻限制 CBOOT 的充电电流,还限制了在上管 Q1 源极的电压负向瞬态时肖特基二极管的电流。

关于圣邦微电子

圣邦微电子(北京)股份有限公司(股票代码 300661)专注于高性能、高品质模拟集成电路的研发和销售。产品覆盖信号链和电源管理两大领域,拥有 30 大类 4600 余款可供销售型号,全部自主研发,广泛应用于工业、汽车电子、通信设备、消费类电子和医疗仪器等领域,以及物联网、新能源和人工智能等新兴市场。